Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Verilog Manual

Caricato da

Shiva Kumar ATitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Verilog Manual

Caricato da

Shiva Kumar ACopyright:

Formati disponibili

“ HDL lab”

1)Verilog pgm to realize all gates

module allgate(a,b,y);

input a,b;

output [1:6] y;

assign y[1]= a & b,

y[2]= a | b,

y[3]= ~a ,

y[4]= ~(a & b),

y[5]= ~(a | b),

y[6]= a ^ b;

endmodule

2) Verilog pgm for binary to gray convertion

module b2g(b,g);

input [3:0] b;

output [3:0] g;

xor (g[0],b[0],b[1]),

(g[1],b[1],b[2]),

(g[2],b[2],b[3]);

assign g[3]=b[3];

endmodule

3)Verilog pgm for 4-bit counter

module cnt4(rst,clk,q);

input rst,clk;

output [3:0] q;

reg[3:0]q;

always @ (posedge clk)

if (rst==0)

q<= 0;

else

q<=q+1;

endmodule

IV Semister Verilog Lab Manual 1 ECEDEPARTMENT,GCE

“ HDL lab”

4) Verilog pgm for comparator

module comp(a,b,aeqb,agtb,altb);

input [3:0] a,b;

output aeqb,agtb,altb;

reg aeqb,agtb,altb;

always @(a or b)

begin

aeqb=0; agtb=0; altb=0;

if(a==b)

aeqb=1;

else if (a>b)

agtb=1;

else

altb=1;

end

endmodule

5)Verilog pgm for asyncronus counter with reset and enable

module count4(clk,resetn,en,q);

input clk,resetn,en;

output q;

reg q;

always@(posedge clk or negedge resetn)

if (resetn==0)

q<=0;

else if(en==1)

q<=q+1;

endmodule

6) verilog pgm for d flip flop

module dff(d,clk,q);

input d,clk;

inout q;

reg q;

always @(posedge clk)

q<=d;

endmodule

IV Semister Verilog Lab Manual 2 ECEDEPARTMENT,GCE

“ HDL lab”

7) verilog pgm for 1 to 8 DEMUX.

module dmux1t8 (I,sel,f);

input I;

input [2:0]sel;

output [7:0]f;

reg [7:0]f;

always@(I or sel)

begin

if(sel==3'b000)

f[7]=I;

else if(sel==3'b001)

f[6]=I;

else if (sel==3'b010)

f[5]=I;

else if (sel==3'b011)

f[4]=I;

else if (sel==3'b100)

f[3]=I;

else if (sel==3'b101)

f[2]=I;

else if (sel==3'b110)

f[1]=I;

else

f[0]=I;

end

endmodule

8) verilog code for full adder structural.

module fa (x,y,z,cout,sum);

input x,y,z;

output cout,sum;

wire P1,P2,P3;

HA HA1 (sum(P1),cout(P2),a(x), b(y));

HA HA2 (sum(sum),carry(P3),a(P1),b(Z));

OR1 ORG (P2,P3, Cout);

Endmodule

IV Semister Verilog Lab Manual 3 ECEDEPARTMENT,GCE

“ HDL lab”

9) verilog code for full adder behavioral.

module fulladd(cin,x,y,s,co);

input cin,x,y;

output s,co;

reg s,co;

always@(cin or x or y)

begin

case ({cin,x,y})

3'b000:{co,s}='b00;

3'b001:{co,s}='b01;

3'b010:{co,s}='b01;

3'b011:{co,s}='b10;

3'b100:{co,s}='b01;

3'b101:{co,s}='b10;

3'b110:{co,s}='b10;

3'b111:{co,s}='b11;

endcase

end

endmodule

10) verilog code for priority encoder

module priority(w,y,f);

input [3:0] w;

output [1:0] y;

output f;

reg [1:0]y;

assign f=(w!=0);

always @(w)

begin

casex(w)

'b1xxx:y=3;

'b1xxx:y=2;

'b1xxx:y=1;

default:y=0;

endcase

end

endmodule

IV Semister Verilog Lab Manual 4 ECEDEPARTMENT,GCE

“ HDL lab”

11) verilog pgm for priority encoder

module priority1(w,y,z);

input [3:0] w;

output [1:0] y;

output z;

reg [1:0] y;

reg z;

always@ (w)

begin

Z='1';

casex(w)

4'b1xxx:y=3;

4'b01xx:y=2;

4'b001x:y=1;

4'b0001:y=0;

default:

begin

Z=='0'

y==2'bx;

end

endcase

end

endmodule

12) verilog pgm for 4-bit updown counter

module updown(r,clk,l,e,u_d,q);

parameter n=8

input [n-1:0]r;

input clk,l,e,u_d;

output [n-1:0]q

reg [n-1:0]q;

integer dir;

always@(posedge clk)

begin

if (u_d)

dir=1;

else

dir=0;

if (l)

q<=r;

else if(e)

q<=Q+dir

end

endmodule

IV Semister Verilog Lab Manual 5 ECEDEPARTMENT,GCE

Potrebbero piacerti anche

- Jupyter TutorialjDocumento20 pagineJupyter Tutorialjshani17% (6)

- Verilog Modules For Common Digital FunctionsDocumento30 pagineVerilog Modules For Common Digital Functionselle868Nessuna valutazione finora

- Following Is The Verilog Code For FlipDocumento26 pagineFollowing Is The Verilog Code For FlipDivya MuraliNessuna valutazione finora

- Python Language For Humans by Christopher TopalianDocumento445 paginePython Language For Humans by Christopher TopalianCollegeOfScriptingNessuna valutazione finora

- Verilog and Test Bench Code For FlipflopsDocumento11 pagineVerilog and Test Bench Code For FlipflopsKeith Fernandes67% (3)

- Digital Hardware Design Assignment: Verilog Codes and SimulationsDocumento16 pagineDigital Hardware Design Assignment: Verilog Codes and SimulationsTeja Krishna Kopuri100% (2)

- Verilog HDL Lectuer 5Documento36 pagineVerilog HDL Lectuer 5Nilesh GulveNessuna valutazione finora

- Verilog ProgramDocumento24 pagineVerilog ProgramRahul BhatiaNessuna valutazione finora

- Verilog FaqDocumento101 pagineVerilog Faqbalashyamu100% (1)

- Exceptions Per CellDocumento3 pagineExceptions Per CellBa Truong HuuNessuna valutazione finora

- VerilogexampleDocumento20 pagineVerilogexampleGayathri SankarNessuna valutazione finora

- Logic Design Lab Verilog 101Documento49 pagineLogic Design Lab Verilog 101杜岳Nessuna valutazione finora

- 1) %%%% Basic Gates %%%%Documento4 pagine1) %%%% Basic Gates %%%%Harsha Vardhan TholetiNessuna valutazione finora

- Verilog Behavioral Program For Counters: Up Counter (4 Bit)Documento17 pagineVerilog Behavioral Program For Counters: Up Counter (4 Bit)Sainadh YerrapragadaNessuna valutazione finora

- CounterDocumento34 pagineCounterAishwarya GajendrulaNessuna valutazione finora

- Verilog CodesDocumento26 pagineVerilog Codesnvrkrishna456Nessuna valutazione finora

- 21BCT0093 VL2022230504083 Ast08Documento15 pagine21BCT0093 VL2022230504083 Ast08Srinivasan UmaNessuna valutazione finora

- Vlsi Comple Lab TaskDocumento37 pagineVlsi Comple Lab TaskTausique SheikhNessuna valutazione finora

- Experiment: 1: ObjectDocumento13 pagineExperiment: 1: ObjectAjay SinghNessuna valutazione finora

- Vlsi Lab ProgramsDocumento14 pagineVlsi Lab ProgramsThirumalai TrendchaserNessuna valutazione finora

- Lab 3 DSDDocumento8 pagineLab 3 DSDRohaidNessuna valutazione finora

- VLSI Lab Manual Exercise ProblemsDocumento38 pagineVLSI Lab Manual Exercise ProblemsPrakhar Kumar100% (1)

- Lab Results VlsiDocumento18 pagineLab Results Vlsipankaj rangareeNessuna valutazione finora

- Eda LabrecordDocumento71 pagineEda Labrecordteja roopNessuna valutazione finora

- Test On Digital Design Using Verilog: Ans: Option CDocumento5 pagineTest On Digital Design Using Verilog: Ans: Option CNarendra Babu GunnamNessuna valutazione finora

- Verilog CodesDocumento26 pagineVerilog CodesmdlogicsolutionsNessuna valutazione finora

- 18ecl58 HDL Lab 2020Documento16 pagine18ecl58 HDL Lab 2020sureshfm170% (10)

- Verilog Modules For Common Digital FunctionsDocumento30 pagineVerilog Modules For Common Digital Functionssudarshan poojaryNessuna valutazione finora

- NC LaunchDocumento40 pagineNC LaunchKamalpreet KaurNessuna valutazione finora

- Vlsi Programs (Ag, CNTRS)Documento3 pagineVlsi Programs (Ag, CNTRS)madhusudhanNessuna valutazione finora

- Verilog Tutorial Mirza A Baig CSE Department YUC Yanbu Industrial City, Saudi ArabiaDocumento14 pagineVerilog Tutorial Mirza A Baig CSE Department YUC Yanbu Industrial City, Saudi ArabiaMirza BaigNessuna valutazione finora

- Verilog Coding ExamplesDocumento41 pagineVerilog Coding ExamplesKarishma PotnuruNessuna valutazione finora

- Verilog Lab SolutionsDocumento15 pagineVerilog Lab Solutionsraja_ramalingam07Nessuna valutazione finora

- VerilogcodeDocumento27 pagineVerilogcodeskrsnaprasadNessuna valutazione finora

- ASIC Design Lab ReportsDocumento16 pagineASIC Design Lab ReportsNisar Ahmed RanaNessuna valutazione finora

- Assignment 1 - ReriewDocumento5 pagineAssignment 1 - ReriewAnh NamNessuna valutazione finora

- Board WorkDocumento51 pagineBoard WorkRama krishna LankaNessuna valutazione finora

- Ver I Log ExamplesDocumento22 pagineVer I Log ExamplesDayanand Gowda KrNessuna valutazione finora

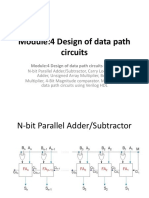

- Module:4 Design of Data Path Circuits 6 HoursDocumento44 pagineModule:4 Design of Data Path Circuits 6 HoursSahana MecheriNessuna valutazione finora

- Verilog Code FAQDocumento25 pagineVerilog Code FAQRAGUL RAJ SNessuna valutazione finora

- Lab1 2Documento6 pagineLab1 2karnikrathva200Nessuna valutazione finora

- Vlsi A & B - 2011Documento70 pagineVlsi A & B - 2011Amaresh RamathalNessuna valutazione finora

- Logic - Output (T) F (Logic - Inputs (T) )Documento23 pagineLogic - Output (T) F (Logic - Inputs (T) )vamsikrishna gollapudiNessuna valutazione finora

- Final VLSI LAB Digital Analog RecordDocumento22 pagineFinal VLSI LAB Digital Analog RecordManjunatha Swamy VNessuna valutazione finora

- Vlsi Part A ProgramsDocumento11 pagineVlsi Part A ProgramsPraveen Kumar RNessuna valutazione finora

- Verilog NotesDocumento41 pagineVerilog NotesJaya SreeNessuna valutazione finora

- Assignment3 2021HT80531Documento14 pagineAssignment3 2021HT80531crypto.investnmentNessuna valutazione finora

- Experiment 21: Design and Simulate 3-Bit Gray Counter Using Verilog HDLDocumento3 pagineExperiment 21: Design and Simulate 3-Bit Gray Counter Using Verilog HDLAbhaySharmaNessuna valutazione finora

- 22BCP367 DECO Assignment 5Documento11 pagine22BCP367 DECO Assignment 5Smit PatelNessuna valutazione finora

- Logic Gates: AIM: To Design Basic Logic Gates Tool Used: CodeDocumento35 pagineLogic Gates: AIM: To Design Basic Logic Gates Tool Used: CodeMALVIKANessuna valutazione finora

- Vlsi 1Documento48 pagineVlsi 1Prasanna ECE 46Nessuna valutazione finora

- HDL Manual (18ecl58)Documento20 pagineHDL Manual (18ecl58)lohith sNessuna valutazione finora

- 22bce20019. Lab Report-DldDocumento40 pagine22bce20019. Lab Report-Dldrockstarguy2005Nessuna valutazione finora

- Module SIPODocumento4 pagineModule SIPOVenkatGollaNessuna valutazione finora

- VERILOG: Synthesis - Combinational Logic Combination Logic Function Can Be Expressed AsDocumento23 pagineVERILOG: Synthesis - Combinational Logic Combination Logic Function Can Be Expressed AsShivangi AgrawalNessuna valutazione finora

- VerilogDocumento6 pagineVerilogShaik IliyasNessuna valutazione finora

- Lab9Documento10 pagineLab9Nrusingha Prasad PandaNessuna valutazione finora

- Assignment-1 & 2 (MST) : Submitted by - Name - Shailendra Yadav - (21DR0165)Documento5 pagineAssignment-1 & 2 (MST) : Submitted by - Name - Shailendra Yadav - (21DR0165)Shailendra YadavNessuna valutazione finora

- Homework #9 SolutionDocumento4 pagineHomework #9 Solutionsanjeewa29Nessuna valutazione finora

- Dwnload Full Digital Systems Design Using Verilog 1st Edition Roth Solutions Manual PDFDocumento35 pagineDwnload Full Digital Systems Design Using Verilog 1st Edition Roth Solutions Manual PDFhaodienb6qj100% (13)

- Sample Eda Lab (Part-A) Manual: Simulation OutputDocumento20 pagineSample Eda Lab (Part-A) Manual: Simulation Outputmdzakir_hussainNessuna valutazione finora

- Package Import Import Import Import Import Public Class Extends Private PrivateDocumento3 paginePackage Import Import Import Import Import Public Class Extends Private Privatejagdish kumarNessuna valutazione finora

- Exercise 3&4Documento3 pagineExercise 3&4alvin sulthanNessuna valutazione finora

- A Game Logic Specification Proposal For 2 D VideogamesDocumento11 pagineA Game Logic Specification Proposal For 2 D VideogamesgokhancantasNessuna valutazione finora

- Final 2 PLSQLDocumento16 pagineFinal 2 PLSQLBadri Mahmoud AliNessuna valutazione finora

- DbmsDocumento74 pagineDbmsGuneet GargNessuna valutazione finora

- Application Based Programming in Python Chapter 2Documento13 pagineApplication Based Programming in Python Chapter 2Womba LukamaNessuna valutazione finora

- Lab 3Documento16 pagineLab 3shameem siddiqueNessuna valutazione finora

- Spring CoremoduleDocumento108 pagineSpring CoremoduleVenkat GowdaNessuna valutazione finora

- Other Relevant Roadmaps: Postgresql Roadmap Backend Developer RoadmapDocumento1 paginaOther Relevant Roadmaps: Postgresql Roadmap Backend Developer RoadmapVăn MinhNessuna valutazione finora

- Aula Ch2 2Documento27 pagineAula Ch2 2Charles ChavesNessuna valutazione finora

- LV Upgrade NotesDocumento12 pagineLV Upgrade NotesAjeet BhartiNessuna valutazione finora

- Ch04 SelectionDocumento28 pagineCh04 SelectionfazumiaNessuna valutazione finora

- 2nd Puc Computer Science Notes PDF (1 Mark Questions and Answers) - 2nd Puc Computer ScienceDocumento11 pagine2nd Puc Computer Science Notes PDF (1 Mark Questions and Answers) - 2nd Puc Computer ScienceMohan Kumar50% (2)

- HMS BrochureDocumento14 pagineHMS BrochureKimNessuna valutazione finora

- Shane Ryan CVDocumento3 pagineShane Ryan CVShaneMRyanNessuna valutazione finora

- Codigo TunstallDocumento5 pagineCodigo TunstallLidia LópezNessuna valutazione finora

- E A Cds V: Mbedded Nalytics IewsDocumento10 pagineE A Cds V: Mbedded Nalytics IewsvenuNessuna valutazione finora

- SLIMalloc: A Safer, Faster, and More Capable Heap AllocatorDocumento16 pagineSLIMalloc: A Safer, Faster, and More Capable Heap AllocatorpierreNessuna valutazione finora

- Art Gallery DatabaseDocumento4 pagineArt Gallery DatabaseBlen TenawNessuna valutazione finora

- WD4A - SmartformsDocumento11 pagineWD4A - SmartformssciucciNessuna valutazione finora

- Course3 Module2 Intro To Hive SlidesDocumento76 pagineCourse3 Module2 Intro To Hive SlidesAnonymous U5zM45uBdNessuna valutazione finora

- FDocumento36 pagineFPeras y ManzanasNessuna valutazione finora

- Chapter 5Documento14 pagineChapter 5Mahir AbrarNessuna valutazione finora

- Q2 MODULE3 G11 .NET PROG MangaldanNHSDocumento10 pagineQ2 MODULE3 G11 .NET PROG MangaldanNHSJensen TagudinNessuna valutazione finora

- Lab 1Documento2 pagineLab 1Nguyễn NhiNessuna valutazione finora

- Cmsis End User Licence AgreementDocumento3 pagineCmsis End User Licence AgreementSindhuja VsNessuna valutazione finora

- Notes 07 Compression PDFDocumento193 pagineNotes 07 Compression PDFhussein hammoudNessuna valutazione finora