Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

8051 Instruction Set Summary

Caricato da

anilshaw27Descrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

8051 Instruction Set Summary

Caricato da

anilshaw27Copyright:

Formati disponibili

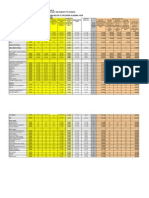

INSTRUCTION SET SUMMARY Page 1

APPENDIX B

INSTRUCTION SET SUMMARY

This appendix contains two tables (see tables B-1 and B-2): the first identifies all of the 8052's instructions in alphabetical order; the second

table lists the instructions according to their hexadecimal opcodes and lists the assembly language instructions that produced that opcode.

The alphabetical listing also includes documentation of the bit pattern, flags affected, number of machine cycles per execution and a

description of the instructions operation and function. The list below defines the conventions used to identify operation and bit patterns.

ABBREVIATIONS AND NOTATIONS USED

A Accumulator llllllll One byte of a 16-bit

AB Register Pair address encoded in

B Multiplication Register operand byte

bit address 8052 bit address mmmmmmmm Data address encoded in

page address 11-bit code address within operand byte

2K page oooooooo Relative offset encoded in

relaVve offset 8-bit 2's complement offset operand byte

C Carry Flag r or rrr Register identifier encoded

code address Absolute code address in operand byte

data Immediate data AND Logical AND

data address On-chip 8-bit RAM address NOT Logical complement

DPTR Data pointer OR Logical OR

PC Program Counter XOR Logical exclusive OR

Rr Register (r = 0-7) + Plus

SP Stack pointer - Minus

high High order byte / Divide

low Low order byte * Multiply

i-j Bits i through j (X) The contents of X

.n Bit n ((X)) The memory location

aaa aaaaaaaa Absolute page address addressed by (X)

encoded in instruction (The contents of X)

and operand byte = Is equal to

bbbbbbbb Bit address encoded in <> Is not equal to

operand byte < Is less than

dddddddd Immediate data encoded in > Is greater than

operand byte <- Is replaced by

Table B-1. Instruction Set Summary

Mnemonic Binary Flags Function

Operation Cycles Code P OV AC C

ACALL code addr 2 a a a 1 0 0 0 1 Push PC on stack, and

(PC) <- (PC) + 2 a a a a a a a a replace low order 11 bits

(SP) <- (SP) + 1 with low order 11 bits of

((SP)) <- (PC) low code address.

(SP) <- (SP) + 1

((SP)) <- (PC) high

(PC) 0-10 <- page address

ADD A,#data 1 0 0 1 0 0 1 0 0 P OV AC C Add immediate data to A.

(A) <- (A) + data d d d d d d d d

ADD A,@Rr 1 0 0 1 0 0 1 1 r P OV AC C Add contents of indirect

(A) <- (A) + ((Rr)) address to A.

ADD A,Rr 1 0 0 1 0 1 r r r P OV AC C Add register to A.

(A) <- (A) + (Rr)

ADD A,data addr 1 0 0 1 0 0 1 0 1 P OV AC C Add contents of data

(A) <- (A) + (data address) m m m m m m m m address to A.

ADDC A,#data 1 0 0 1 1 0 1 0 0 P OV AC C Add C and immediate data

(A) <- (A) + (C) + data d d d d d d d d to A

ADDC A,@Rr 1 0 0 1 1 0 1 1 r P OV AC C Add C and contents of

(A) <- (A) + (C) + ((Rr)) indirect address to A.

ADDC A,Rr 1 0 0 1 1 1 r r r P OV AC C Add C and register to A

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 2

(A) <- (A) + (C) + (Rr)

ADDC A,data addr 1 0 0 1 1 0 1 0 1 P OV AC C Add C and contents of data

(A) <- (A) + (C) + (data address) m m m m m m m m address to A

AJMP code addr 2 a a a 0 0 0 0 1 Replace low order 11 bits of

(PC) 0-10 <- code address a a a a a a a a PC with low order 11 bits

code address.

ANL A,#data 1 0 1 0 1 0 1 0 0 P Logical AND immediate data

(A) <- (A)AND data d d d d d d d d to A.

ANL A,@Rr 1 0 1 0 1 0 1 1 r P Logical AND contents of

(A) <- (A) AND ((Rr)) indirect address to A

ANL A,Rr 1 0 1 0 1 1 r r r P Logical AND register to A

(A) <- (A) AND (Rr)

ANL A,data addr 1 0 1 0 1 0 1 0 1 P Logical AND contents of

(A) <- (A) AND (data address) m m m m m m m m data address to A.

ANL C,bit addr 2 1 0 0 0 0 0 1 0 C Logical AND bit to C

(C) <- (C) AND (bit address) b b b b b b b b

ANL C,lbit addr 2 1 0 1 1 0 0 0 0 C Logical AND complement of

(C) <- (C) AND NOT (bit address) b b b b b b b b bit to C

ANL data addr, #data 2 0 1 0 1 0 0 1 1 Logical AND immediate data

(data address) <- m m m m m m m m to contents of data address

(data address) AND data d d d d d d d d

ANL data addr,A 1 0 1 0 1 0 0 1 0 Logical AND A to contents of

(data address) <- m m m m m m m m data address.

(data address) AND A

CJNE @Rr,#data,code addr 2 1 0 1 1 0 1 1 r C If immediate data and

(PC)<- (PC) + 3 d d d d d d d d contents of indirect address

IF ((Rr)) < > data o o o o o o o o are not equal, jump to code

THEN address.

(PC) <- (PC) + relative offset

IF ((Rr)) <data

THEN(C) <- 1

ELSE(C) <- 0

CJNE A,#data,code addr 2 1 0 1 1 0 1 0 0 C If immediate data and A are

(PC) <- (PC) + 3 d d d d d d d d not equal, jump to code

IF(A)<>data o o o o o o o o address.

THEN

(PC) <- (PC) + relative offset

IF (A) <data

THEN(C) <- 1

ELSE(C) <- 0

CJNE A,data addr,code addr 2 1 0 1 1 0 1 0 1 C If contents of data address

(PC) <- (PC) + 3 m m m m m m m m and A are not equal, jump to

IF (A) <> (data address) o o o o o o o o code address.

THEN

(PC) <- (PC) + relative offset

IF (A) < (data address)

THEN(C) <- 1

ELSE(C) <- 0

CJNE Rr,#data,code addr 2 1 0 1 1 1 r r r C If immediate data and

(PC) <- (PC) + 3 d d d d d d d d register are not equal, jump

IF (Rr) <> data o o o o o o o o to code address.

THEN

(PC) <- (PC) + relative offset

IF (Rr) < data

THEN(C) <- 1

ELSE(C) <- 0

CLR A 1 1 1 1 0 0 1 0 0 P Set A to zero(O).

(A) <- 0

CLR C 1 1 1 0 0 0 01 1 C Set C to zero (0).

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 3

(C) <- 0

CLR bit addr 1 1 1 0 0 0 0 1 0 Set bit to zero (0).

(bit address) <- 0 b b b b b b b b

CPL A 1 1 1 1 1 0 1 0 0 P Complements each bit in A.

(A) <- NOT (A)

CPL C 1 1 0 1 1 0 0 1 1 C Complement C.

(C) <- NOT (C)

CPL bit addr 1 1 0 1 1 0 0 1 0 Complement bit.

(bitaddress) <- b b b b b b b b

NOT (bit address)

DA A 1 1 1 0 1 0 1 0 0 P C Adjust A after a BCD add.

DEC @Rr 1 0 0 0 1 0 1 1 r Decrement contents of

((Rr)) <- ((Rr)) - 1 indirect address.

DEC A 1 0 0 0 1 0 1 0 0 P Decrement A.

(A) <- (A) - 1

DEC Rr 1 0 0 0 1 1 r r r Decrement register.

(Rr) <- (Rr) -1

DEC data addr 1 0 0 0 1 0 1 0 1 Decrement contents of data

(data address) <- m m m m m m m m address.

(data address) - 1

DIV AB 4 1 0 0 0 0 1 0 0 P OV C Divide A by B (multiplication

(AB) <- (AJ/(B) register).

DJNZ Rr,code addr 2 1 1 0 1 1 r r r Decrement register, if not

(PC) <- (PC) + 2 o o o o o o o o zero (0), then jump to code

(Rr) <- (Rr) - 1 address.

IF(Rr)<>0

THEN

(PC) <- (PC) + relative offset

DJNZ data addr,code addr 2 1 1 0 1 0 1 0 1 Decrement data address, if

(PC), <- (PC) + 3 m m m m m m m m zero (0), then jump to code

(data address)<-( o o o o o o o o address.

(data address) - 1

IF (data address) <> 0

THEN

(PC) <- (PC) + relative offset

INC @Rr 1 0 0 0 0 0 1 1 r Increment contents of

((Rr)) <- ((Rr)) + 1 indirect address.

INC A 1 0 0 0 0 0 1 0 0 P Increment A.

(A) <- (A) + 1

INC DPTR 1 1 0 1 0 0 0 1 1 Increment 16-bit data

(DPTR) <- (DPTR) + 1 pointer.

INC Rr 1 0 0 0 0 1 r r r Increment register.

((R) <- (Rr) + 1

INC data addr 2 0 0 0 0 0 1 0 1 Increment contents of data

(data address) <- m m m m m m m m address.

(data address) + 1

JB bit addr,code addr 2 0 0 1 0 0 0 0 0 If bit is one, n jump to code

(PC) <- (PC) + 3 b b b b b b b b address.

IF (bit address) = 1 o o o o o o o o

THEN

(PC) <- (PC) + relative offset

JBC bit addr,code addr 2 0 0 0 1 0 0 0 0 If bit is one, n clear bit and

(PC) <- (PC) + 3 b b b b b b b b jump to code address.

IF (bit address) = 1 o o o o o o o o

THEN

(bit address) <- 0

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 4

(PC) <- (PC) + relative offset

JC code addr 2 0 1 0 0 0 0 0 0 If C is one, then jump to

(PC) (PC) + 2 o o o o o o o o code address.

IF(C) = 1

THEN

(PC) <- (PC) + relative offset

JMP @A + DPTR 2 0 1 1 1 0 0 1 1 Add A to data pointer and

(PC) <- (A) + (DPTR) jump to that code address.

JNB bit addr,code addr 2 0 0 1 1 0 0 0 0 If bit is zero, n jump to code

(PC) <- (PC) + 3 b b b b b b b b address.

IF (bit address) = 0 o o o o o o o o

THEN

(PC) <- (PC) + relative offset

JNC code addr 2 0 1 0 1 0 0 0 0 If C is zero (0), n jump to

(PC) + (PC) + 2 o o o o o o o o code address.

IF (C) = 0

THEN

(PC) <- (PC) + relative offset

JNZ code addr 2 0 1 1 1 0 0 0 0 If A is not zero (0), n jump

to

(PC) <- (PC) + 2 o o o o o o o o code address.

IF (A) <> 0

THEN

(PC) <- (PC) + relative offset

JZ code addr 2 0 1 1 0 0 0 0 0 If A is zero (0), then jump to

(PC) <- (PC) + 2 o o o o o o o o code address.

IF (A) = 0

THEN

(PC) <- (PC) + relative offset

LCALL code addr 2 0 0 0 1 0 0 1 0 Push PC on stack and

(PC) <- (PC) + 3 1 1 1 1 1 1 1 1 + replace entire PC value with

(SP) <- (SP) + 1 1 1 1 1 1 l 1 1 + code address.(1)

((SP)) <- ((PC)) low

(SP) <- (SP) + 1

((SP)) <- (PC) high

(PC) <- code address

LJMP code addr 2 0 0 0 0 0 0 1 0 Jump to code address.(1)

(PC) <- code address 1 1 1 1 1 1 1 1 +

1 1 1 1 1 1 1 1 +

MOV @Rr,#data 1 0 1 1 1 0 1 1 r Move immediate data to

((Rr)) <- data d d d d d d d d indirect address.

MOV @Rr,A 1 1 1 1 1 0 1 1 r Move A to indirect address.

((Rr)) <- (A)

MOV @Rr,data addr 2 1 0 1 0 0 1 1 r Move contents of data

((Rr)) <- (data address) m m m m m m m m address to indirect address.

MOV A,#data 1 0 1 1 1 0 1 0 0 P Move immediate data to A.

(A) <- data d d d d d d d d

MOV A,@Rr 1 1 1 1 0 0 1 1 r P Move contents of indirect

(A) -< ((Rr)) address to A.

MOV A,Rr 1 1 1 1 0 1 r r r P Move register to A.

(A) <- (Rr)

MOV A,data addr 1 1 1 1 0 0 1 0 1 P Move contents of data

(A) <- (data address) m m m m m m m m address to A.

MOV C,bit addr 1 1 0 1 0 0 0 1 0 C Move bit to C.

(C) <- (bitaddress) b b b b b b b b

MOV DPTR,#data 2 1 0 0 1 0 0 0 0 Move two bytes of

(DPTR) <- data d d d d d d d d + immediate data pointer.(1)

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 5

d d d d d d d d +

MOV Rr,#data 1 0 1 1 1 1 r r r Move immediate data to

(Rr) <- data d d d d d d d d register.

MOV Rr,A 1 1 1 1 1 1 r r r Move A to register.

(Rr) <- (A)

MOV Rr,data addr 2 1 0 1 0 1 r r r Move contents of data

(Rr) <- (data address) m m m m m m m m address to register.

MOV bit addr,C 2 1 0 0 1 0 0 1 0 Move C to bit.

(bit address) <- (C) b b b b b b b b

MOV data addr,#data 2 0 1 1 1 0 1 0 1 Move immediate data to data

(data address) <- data m m m m m m m m address.

d d d d d d d d

MOV data addr,@Rr 2 1 0 0 0 0 1 1 r Move contents of indirect

(data address) <- ((Rr)) m m m m m m m m address to data address.

MOV data addr,A 1 1 1 1 1 0 1 0 1 Move A to data address.

(data address) <- (A) m m m m m m m m

MOV data addr,Rr 2 1 0 0 0 1 r r r Move register to data

(data address) <- (Rr) m m m m m m m m address.

MOV data addr1,data addr2 2 1 0 0 0 0 1 0 1 Move contents of second

(data address1) <- m m m m m m m m + data address to first data

(data address2) m m m m m m m m + address.(2)

MOVC A,@A + DPTR 2 1 0 0 1 0 0 1 1 P Add A to DPTR and move

(PC) <- (PC) + 1 contents of that code

(A) <- ((A) + (DPTR)) address with A.

MOVC A,@A + PC 2 1 0 0 0 0 0 1 1 P Add A to PC and move

(A) <- ((A) + (PC)) contents of that code

address with A.

MOVX @DPTR,A 2 1 1 1 1 0 0 0 0 Move A to external data

DPTR)) <- (A) location addressed by

DPTR.

MOVX @Rr,A 2 1 1 1 1 0 0 1 r Move A to external data

((Rr)) <- (A) location addressed by

reglster.

MOVX A,@DPTR 2 1 1 1 0 0 0 0 0 P Move contents of external

(A) <- ((DPTR)) data location addressed by

DPTR to A

MOVX A,@Rr 2 1 1 1 0 0 0 1 r P Move contents of external

(A) <- ((Rr)) data location addressed by

reglster to A.

MUL AB 4 1 0 1 0 0 1 0 0 P OV C Multiply A by B

(AB) <- (A) * (B) (multiplication register).

NOP 1 0 0 0 0 0 0 0 0 Do nothing.

ORL A,#data 1 0 1 0 0 0 1 0 0 P Logical OR immediate data

(A) <- (A)OR data d d d d d d d d toA.

ORL A,@Rr 1 0 1 0 0 0 1 1 r P Logical OR contents of

(A) <- (A) OR ((Rr)) indirect address to A

ORL A,Rr 1 0 1 0 0 1 r r r P Logical OR register to A

(A) <- (A) OR (Rr)

ORL A,data addr 1 0 1 0 0 0 1 0 1 P Logical OR contents of data

(A) <- (A) OR (data address) m m m m m m m m address to A.

ORL C,bit addr 2 0 1 1 1 0 0 1 0 C Logical OR bit to C

(C) <- (C) OR (bit address) b b b b b b b b

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 6

ORL C,/bit addr 2 1 0 1 0 0 0 0 0 C Logical OR complement of

(C) <- (C) OR NOT (bit address) b b b b b b b b bit to C.

ORL data addr,#data 2 0 1 0 0 0 0 1 1 Logical OR immediate data

(data address) <- m m m m m m m m to data address.

(dataaddress)ORdata d d d d d d d d

ORL data addr,A 1 0 1 0 0 0 0 1 0 Logical OR A to data

(data address) <- m m m m m m m m address.

(data address) OR A

POP data addr 2 1 1 0 1 0 0 0 0 Place top of stack at data

(data address) <- ((SP)) m m m m m m m m address and decrement SP.

(SP) <- (SP) - 1

PUSH data addr 2 1 1 0 0 0 0 0 0 Increment SP and place

(SP) <- (SP) + 1 m m m m m m m m contents of data address at

((SP)) <- (data address) top of stack.

RET 2 0 0 1 0 0 0 1 0 Return from subroutine call.

(PC)high <- ((SP))

(SP) <- (SP) - 1

(PC)low <- ((SP))

(SP) <- (SP) - 1

RETI 2 0 0 1 1 0 0 1 0 Return from interrupt routine.

(PC)high <- ((SP))

(SP) <- (SP) - 1

(PC)low <- ((SP))

(SP) <- (SP)

RL A 1 0 0 1 0 0 0 1 1 Rotate A left one position.

RLC A 1 0 0 1 1 0 0 1 1 P C Rotate A through C left one

position.

RR A 1 0 0 0 0 0 0 1 1 Rotate A right one position.

RRC A 1 0 0 0 1 0 0 1 1 P C Rotate A through C right one

position.

SETB C 1 1 1 0 1 0 0 1 1 C Set C to one (1).

(C) <- 1

SET8 bit addr 1 1 1 0 1 0 0 1 0 Set bit to one (1).

(bit address) <- 1 b b b b b b b b

SJMP code addr 2 1 0 0 0 0 0 0 0 Jump to code address.

(PC) <- (PC) + 2 o o o o o o o o

(PC) <- (PC) + relative offset

SUBB A,#data 1 1 0 0 1 0 1 0 0 P OV AC C Subtract immediate data

(A) <- (A) - (C) - data d d d d d d d d from A.

SUBB A,@Rr 1 1 0 0 l 0 l l r P OV AC C Subtract contents of indirect

(A) <- (A) - (C) - ((Rr)) address from A.

SUBB A,Rr 1 1 0 0 1 1 r r r P OV AC C Subtract register from A.

(A) <- (A) - (C) - (Rr)

SUBB A, data addr 1 1 0 0 1 0 1 0 1 P OV AC C Subtract contents of data

(A) <- (A) - (C) - (data address) m m m m m m m m address from A

SWAP A 1 1 1 0 0 0 1 0 0 Exchange low order nibble

with high order nibble in A

XCH A,@Rr 1 1 1 0 0 0 1 1 r P Move A to indirect address

temp <- ((Rr)) and vice versa.

((Rr)) <- (A)

(A) <- temp

XCH A,Rr 1 1 1 0 0 1 r r r P Move A to register and vice

temp <- (Rr) versa.

(Rr) <- (A)

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 7

(A) <- temp

XCH A,data addr 1 1 1 0 0 0 1 0 1 P Move A to data address and

temp <- (data address) m m m m m m m m vice versa.

(data address) <- (A)

(A) <- temp

XCHD A,@Rr 1 0 1 1 0 0 1 1 r P Move low order of A to low

temp <- ((Rr)) 0-3 order nibble of indirect

((Rr)) 0-3 <- (A) 0-3 address and vice versa.

(A) 0-3 <- temp

XRL A,#data 1 0 1 1 0 0 1 0 0 P Logical exclusive OR

(A) <- (A) XOR data d d d d d d d d immediate data to A

XRL A,@Rr 1 0 1 1 0 0 1 1 r P Logical exclusive OR

(A) <- (A) XOR ((Rr)) contents of indirect address

to A.

XRL A,Rr 1 0 1 1 0 1 r r r P Logical exclusive OR register

(A) <- (A) XOR (Rr) to A.

XRL A,data addr 1 0 1 1 0 0 1 0 1 P Logical exclusive OR

(A) <- (A) XOR (data address) m m m m m m m m contents of data address to A.

XRL data addr,#data 2 0 1 1 0 0 0 1 1 Logical exclusive OR

(data address) <- m m m m m m m m immediate data to data

(data address) XOR data d d d d d d d d address.

XRL data addr,A 1 0 1 1 0 0 0 1 0 Logical exclusive OR A to

(data address) <- m m m m m m m m data address.

(data addr as) XOR A

1)The high order byte of the 16-bit operand is in the first byte following the opcode. The low order byte is in the second byte following the

opcode.

2) The source data address (second data address) is encoded in the first byte following the opcode. The destination data address is encoded

in the second byte following the opcode.

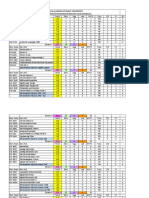

Table B-2. Instruction Opcodes in Hexadecimal

Hex Number Mnemonic Operands

Code of Bytes

00 1 NOP

01 2 AJMP code addr

02 3 LJMP code addr

03 1 RR A

04 1 INC A

05 2 INC data addr

06 1 INC @R0

07 1 INC @R1

08 1 INC R0

09 1 INC R1

0A 1 INC R2

0B 1 INC R3

0C 1 INC R4

0D 1 INC R5

0E 1 INC R6

0F 1 INC R7

10 3 JBC bit addr,code addr

11 2 ACALL code addr

12 3 LCALL code addr

18 1 RRC A

14 1 DEC A

15 2 DEC data addr

16 1 DEC @R0

17 1 DEC @R1

18 1 DEC R0

19 1 DEC R1

1A 1 DEC R2

1B 1 DEC R3

1C 1 DEC R4

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 8

1D 1 DEC R5

1E 1 DEC R6

1F 1 DEC R7

20 3 JB bit addr,code addr

21 2 AJMP code addr

22 1 RET

23 1 RL A

24 2 ADD A,#data

25 2 ADD A,data addr

26 1 ADD A,@R0

27 1 ADD A,@R1

28 1 ADD A,R0

29 1 ADD A,R1

2A 1 ADD A,R2

2B 1 ADD A,R3

2C 1 ADD A,R4

2D 1 ADD A,R5

2E 1 ADD A,R6

2F 1 ADD A,R7

80 3 JNB bit addr,code addr

31 2 ACALL code addr

32 1 RETI

83 1 RLC A

34 2 ADDC A,#data

35 2 ADDC A,data addr

36 1 ADDC A,@R0

37 1 ADDC A,@R1

38 1 ADDC A,R0

89 1 ADDC A,R1

3A 1 ADDC A,R2

3B 1 ADDC A,R3

3C 1 ADDC A,R4

3D 1 ADDC A,R5

3E 1 ADDC A,R7

3F 1 ADDC A,R7

40 2 JC code addr

41 2 AJMP code addr

42 2 ORL data addr,A

43 3 ORL data addr,#data

44 2 ORL A,#data

45 2 ORL A,data addr

46 1 ORL A,@R0

47 1 ORL A,@R1

48 1 ORL A,R0

49 1 ORL A,R1

4A 1 ORL A,R2

4B 1 ORL A,R3

4C 1 ORL A,R4

4D 1 ORL A,R5

4E 1 ORL A,R6

4F 1 ORL A,R7

50 2 JNC code addr

51 2 ACALL code addr

52 2 ANL data addr,A

53 3 ANL data addr,#data

54 2 ANL A,#data

55 2 ANL A,data addr

56 1 ANL A,@R0

57 1 ANL A,@R1

58 1 ANL A,R0

59 1 ANL A,R1

5A 1 ANL A,R2

5B 1 ANL A,R3

5C 1 ANL A,R4

5D 1 ANL A,R5

5E 1 ANL A,R6

5F 1 ANL A,R7

60 2 JZ code addr

61 2 AJMP code addr

62 2 XRL data addr,A

63 3 XRL data addr,#data

64 2 XRL A,#data

65 2 XRL A,data addr

66 1 XRL A,@R0

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 9

67 1 XRL A,@R1

68 1 XRL A,R0

69 1 XRL A,R1

6A 1 XRL A,R2

6B 1 XRL A,R3

6C 1 XRL A,R4

6D 1 XRL A,R5

6E 1 XRL A,R6

6F 1 XRL A,R7

70 2 JNZ code addr

71 2 ACALL code addr

72 2 ORL C,bit addr

73 1 JMP @A + DPTR

74 2 MOV A,#data

75 3 MOV data addr.#data

76 2 MOV @R0,#data

77 2 MOV @R1,#data

78 2 MOV R0,#data

79 2 MOV R1,#data

7A 2 MOV R2,#data

7B 2 MOV R3,#data

7C 2 MOV R4,#data

7D 2 MOV R5,#data

7E 2 MOV R6,#data

7F 2 MOV R7,#data

80 2 SJMP code addr

81 2 AJMP code addr

82 2 ANL C,bit addr

83 1 MOVC A,@A + PC

84 1 DIV AB

85 3 MOV data addr,data addr

86 2 MOV data addr,@R0

87 2 MOV data addr,@R1

88 2 MOV data addr,R0

89 2 MOV data addr,R1

8A 2 MOV data addr,R2

8B 2 MOV data addr,R3

8C 2 MOV data addr,R4

8D 2 MOV data addr,R5

8E 2 MOV data addr,R6

8F 2 MOV data addr,R7

90 3 MOV DPTR,#data

91 2 ACALL code addr

92 2 MOV bit addr,C

93 1 MOVC A,@A + DPTR

94 2 SUBB A,#data

95 2 SUBB A,data addr

96 1 SUBB A,@R0

97 1 SUBB A,@R1

98 1 SUBB A,R0

99 1 SUBB A,R1

9A 1 SUBB A,R2

9B 1 SUBB A,R3

9C 1 SUBB A,R4

9D 1 SUBB A,R5

9E 1 SUBB A,R6

9F 1 SUBB A,R7

A0 2 ORL C,lbit addr

A1 2 AJMP code addr

A2 2 MOV C,bit addr

A3 1 INC DPTR

A4 1 MUL AB

A5 reserved

A6 2 MOV @R0,data addr

A7 2 MOV @R1,data addr

A8 2 MOV R0,data addr

A9 2 MOV R1,data addr

AA 2 MOV R2,data addr

AB 2 MOV R3,data addr

AC 2 MOV R4,data addr

AD 2 MOV R5,data addr

AE 2 MOV R6,data addr

AF 2 MOV R7,data addr

B0 2 ANL C,lbit addr

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 10

B1 2 ACALL code addr

B2 2 CPL bit addr

B3 1 CPL C

B4 3 CJNE A,#data,code addr

B5 3 CJNE A,data addr,code addr

B6 3 CJNE @R0,#data,code addr

B7 3 CJNE @R1,#data,code addr

B8 3 CJNE RO,#data,code addr

B9 3 CJNE R1,#data,code addr

BA 3 CJNE R2,#data,code addr

BB 3 CJNE R3,#data,code addr

BC 3 CJNE R4,#data,code addr

BD 3 CJNE R5,#data,code addr

BE 3 CJNE R6,#data,code addr

BF 3 CJNE R7,#data,code addr

C0 2 PUSH data addr

C1 2 AJMP code addr

C2 2 CLR bitaddr

C3 1 CLR C

C4 1 SWAP A

C5 2 XCH A,data addr

C6 1 XCH A,@R0

C7 1 XCH A,@R1

C8 1 XCH A,R0

C9 1 XCH A,R1

CA 1 XCH A,R2

CB 1 XCH A,R3

CC 1 XCH A,R4

CD 1 XCH A,R5

CE 1 XCH A,R6

CF 1 XCH A,R7

D0 2 POP data addr

D1 2 ACALL code addr

D2 2 SETB bit addr

D3 1 SETB C

D4 1 DA A

D5 3 DJNZ data addr,code addr

D6 1 XCHD A,@R0

D7 1 XCHD A,@R1

D8 2 DJNZ R0,code addr

D9 2 DJNZ R1,code addr

DA 2 DJNZ R2,code addr

DB 2 DJNZ R3,code addr

DC 2 DJNZ R4,code addr

DD 2 DJNZ R5,code addr

DE 2 DJNZ R6,code addr

DF 2 DJNZ R7,code addr

E0 1 MOVX A,@DPTR

E1 2 AJMP code addr

E2 1 MOVX A,@R0

E3 1 MOVX A,@R1

E4 1 CLR A

E5 2 MOV A,data addr

E6 1 MOV A,@R0

E7 1 MOV A,@R1

E8 1 MOV A,R0

E9 1 MOV A,R1

EA 1 MOV A, R2

EB 1 MOV A,R3

EC 1 MOV A,R4

ED 1 MOV A,R5

EE 1 MOV A,R6

EF 1 MOV A,R7

F0 1 MOVX @DPTR,A

F1 2 ACALL code addr

F2 1 MOVX @R0,A

F3 1 MOVX @R1,A

F4 1 CPL A

F5 2 MOV data addr,A

F6 1 MOV @R0,A

F7 1 MOV @R1,A

F8 1 MOV R0,A

F9 1 MOV R1,A

FA 1 MOV R2,A

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

INSTRUCTION SET SUMMARY Page 11

FB 1 MOV R3,A

FC 1 MOV R4,A

FD 1 MOV R5,A

FE 1 MOV R6,A

FF 1 MOV R7,A

http://www.nomad.ee/micros/bas52man/appb.html 10/20/2008 04:59:25 PM

Potrebbero piacerti anche

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- Web Scraping C18Documento35 pagineWeb Scraping C1819-5E8 Tushara PriyaNessuna valutazione finora

- Satlie Comm PDFDocumento7 pagineSatlie Comm PDFBiju Gopi ThilakaNessuna valutazione finora

- ITNE3006 Design Network Infrastructure: AssignmentDocumento12 pagineITNE3006 Design Network Infrastructure: Assignmentqwerty100% (1)

- FM Create URL For PDF Display in UI5Documento3 pagineFM Create URL For PDF Display in UI5nirav487Nessuna valutazione finora

- Invensys Controls Courses CatalogueDocumento103 pagineInvensys Controls Courses CatalogueNiyi AdetunjiNessuna valutazione finora

- Data UploadDocumento2 pagineData Uploadanilshaw27Nessuna valutazione finora

- Partial Differential Equations: Analytical and Numerical MethodsDocumento136 paginePartial Differential Equations: Analytical and Numerical MethodsMohamed Mounir FekriNessuna valutazione finora

- Data 2Documento1 paginaData 2anilshaw27Nessuna valutazione finora

- DataDocumento1 paginaDataanilshaw27Nessuna valutazione finora

- 1031 - Application FormDocumento3 pagine1031 - Application Formanilshaw27Nessuna valutazione finora

- Data UploadiiDocumento1 paginaData Uploadiianilshaw27Nessuna valutazione finora

- Data 4551uploadDocumento2 pagineData 4551uploadanilshaw27Nessuna valutazione finora

- Data UploadDocumento2 pagineData Uploadanilshaw27Nessuna valutazione finora

- Data UploadDocumento2 pagineData Uploadanilshaw27Nessuna valutazione finora

- Data UploadDocumento1 paginaData Uploadanilshaw27Nessuna valutazione finora

- Data UploajjdDocumento1 paginaData Uploajjdanilshaw27Nessuna valutazione finora

- Data V Table1Documento3 pagineData V Table1anilshaw27Nessuna valutazione finora

- Data Upl65oadDocumento2 pagineData Upl65oadanilshaw27Nessuna valutazione finora

- Data UploakodDocumento1 paginaData Uploakodanilshaw27Nessuna valutazione finora

- Visitor's VisaDocumento2 pagineVisitor's Visaanilshaw27Nessuna valutazione finora

- Admission AdvertisementDocumento4 pagineAdmission AdvertisementGhosh SurojitNessuna valutazione finora

- WB MDocumento18 pagineWB Manilshaw27Nessuna valutazione finora

- 1st NKN Public Lecture Poster PDFDocumento1 pagina1st NKN Public Lecture Poster PDFanilshaw27Nessuna valutazione finora

- FCI RecruitmentDocumento36 pagineFCI RecruitmentHsamb AbmNessuna valutazione finora

- Direct Admission - B. TechDocumento2 pagineDirect Admission - B. Techanilshaw27Nessuna valutazione finora

- 0601185Documento14 pagine0601185anilshaw27Nessuna valutazione finora

- Flower PotDocumento4 pagineFlower Potanilshaw27Nessuna valutazione finora

- 24 Sept 2012 ScheduleDocumento5 pagine24 Sept 2012 Scheduleanilshaw27Nessuna valutazione finora

- Extension of Pmegp DateDocumento1 paginaExtension of Pmegp Dateanilshaw27Nessuna valutazione finora

- SwadharDocumento32 pagineSwadharShailander Singh100% (1)

- TR 99 27Documento9 pagineTR 99 27anilshaw27Nessuna valutazione finora

- Tezpur University French Exam Results June 2012Documento2 pagineTezpur University French Exam Results June 2012anilshaw27Nessuna valutazione finora

- Costs 2013Documento6 pagineCosts 2013Sehar AhmedNessuna valutazione finora

- PHD FinalDocumento8 paginePHD Finalanilshaw27Nessuna valutazione finora

- Ready To Send Revised Sci Comm ProgDocumento4 pagineReady To Send Revised Sci Comm Proganilshaw27Nessuna valutazione finora

- LogDocumento12 pagineLogJonalyn C.SallesNessuna valutazione finora

- SPN9971 Mosfet Radio SurDocumento10 pagineSPN9971 Mosfet Radio Surroberto caiadoNessuna valutazione finora

- Componet of A Computer SystemDocumento13 pagineComponet of A Computer System✬ SHANZA MALIK ✬Nessuna valutazione finora

- LM356Documento25 pagineLM356Wilfredo Paniagua OrellanaNessuna valutazione finora

- Qt1314 CA l1p3 Microwave CircuitsDocumento70 pagineQt1314 CA l1p3 Microwave CircuitsDenis CarlosNessuna valutazione finora

- Totalizer FT 100iDocumento6 pagineTotalizer FT 100iAgeng Firstyan BagaskoroNessuna valutazione finora

- AZ324 Quad Op Amp Data SheetDocumento13 pagineAZ324 Quad Op Amp Data SheetAbdoNessuna valutazione finora

- IT Classified PPDocumento154 pagineIT Classified PPfarisashraf04Nessuna valutazione finora

- RTL 8139 ADocumento6 pagineRTL 8139 AEmílio FerroNessuna valutazione finora

- 03TaskPerformance1 PECHONDocumento4 pagine03TaskPerformance1 PECHONAbug Jaime Jr.Nessuna valutazione finora

- HwcompatDocumento462 pagineHwcompatErick CardosoNessuna valutazione finora

- EtnaDocumento2 pagineEtnaREAL20Nessuna valutazione finora

- Class 12 Physic Project On Logic Gates and ICDocumento20 pagineClass 12 Physic Project On Logic Gates and ICRuba VigneshNessuna valutazione finora

- Experiment 10: Implementation of Income Tax/loan EMI Calculator and Deploy The Same On Real DevicesDocumento9 pagineExperiment 10: Implementation of Income Tax/loan EMI Calculator and Deploy The Same On Real DevicesSHUBHANKAR KANOJE100% (1)

- CURS 6 Protocoale FireDocumento38 pagineCURS 6 Protocoale FireCosmina DulhanNessuna valutazione finora

- Ders Kodu Ders Adı Kredi Ders Uyg Lab Akts Türü Z/S YY DilDocumento27 pagineDers Kodu Ders Adı Kredi Ders Uyg Lab Akts Türü Z/S YY DilErdem UsluNessuna valutazione finora

- Media Provider Process Log AnalysisDocumento4 pagineMedia Provider Process Log AnalysisIlhaCikaRahimNessuna valutazione finora

- Hikvision IVMS 4200 PC User ManualDocumento291 pagineHikvision IVMS 4200 PC User ManualMaxim 10Nessuna valutazione finora

- Transmisor Can TJA 1055Documento27 pagineTransmisor Can TJA 1055Revelino Arenas PNessuna valutazione finora

- Spool AdministrationDocumento5 pagineSpool AdministrationKola K SivaramNessuna valutazione finora

- Sourcery G++ Lite 2008q3-72 Getting-StartedDocumento62 pagineSourcery G++ Lite 2008q3-72 Getting-StartedvishwaParamNessuna valutazione finora

- Foxboro FPS400 24 Manual 2016317141433Documento86 pagineFoxboro FPS400 24 Manual 2016317141433modsimcaNessuna valutazione finora

- Manual de Usuario Tarjeta Madre GigaByte GA-990FXA-UD3 v.3.0Documento104 pagineManual de Usuario Tarjeta Madre GigaByte GA-990FXA-UD3 v.3.0Sexto SemestreNessuna valutazione finora

- Smart Bus RMCR7 WebDocumento111 pagineSmart Bus RMCR7 WebEder Alonso Cardenas CepedaNessuna valutazione finora

- Digital day time switch operating guideDocumento4 pagineDigital day time switch operating guideAnonymous IN80L4rR0% (3)