Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

PDF Intersil 45646

Caricato da

henryCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

PDF Intersil 45646

Caricato da

henryCopyright:

Formati disponibili

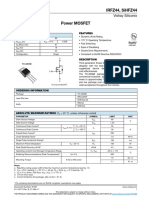

RFG50N06LE, RFP50N06LE, RF1S50N06LESM

Data Sheet

October 1999

50A, 60V, 0.022 Ohm, Logic Level

N-Channel Power MOSFETs

File Number

4072.3

Features

50A, 60V

These N-Channel enhancement mode power MOSFETs are

manufactured using the latest manufacturing process

technology. This process, which uses feature sizes

approaching those of LSI circuits, gives optimum utilization

of silicon, resulting in outstanding performance. They were

designed for use in applications such as switching

regulators, switching converters, motor drivers, and relay

drivers. These transistors can be operated directly from

integrated circuits.

rDS(ON) = 0.022

Temperature Compensating PSPICE Model

Peak Current vs Pulse Width Curve

UIS Rating Curve

175oC Operating Temperature

Formerly developmental type TA49164.

Related Literature

- TB334 Guidelines for Soldering Surface Mount

Components to PC Boards

Ordering Information

Symbol

PART NUMBER

PACKAGE

BRAND

RFG50N06LE

TO-247

FG50N06L

RFP50N06LE

TO-220AB

FP50N06L

RF1S50N06LESM

TO-263AB

F50N06LE

NOTE: When ordering, use the entire part number. Add the suffix 9A

to obtain the TO-263AB variant in tape and reel, i.e.

RF1S50N06LESM9A.

Packaging

JEDEC STYLE TO-247

JEDEC TO-220AB

SOURCE

DRAIN

GATE

SOURCE

DRAIN

GATE

DRAIN

(BOTTOM

SIDE METAL)

DRAIN (FLANGE)

JEDEC TO-263AB

DRAIN

(FLANGE)

GATE

SOURCE

CAUTION: These devices are sensitive to electrostatic discharge; follow proper ESD Handling Procedures.

PSPICE is a registered trademark of MicroSim Corporation.

www.intersil.com or 407-727-9207 | Copyright Intersil Corporation 1999

RFG50N06LE, RFP50N06LE, RF1S50N06LESM

Absolute Maximum Ratings

TC = 25oC, Unless Otherwise Specified

Drain to Source Voltage (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VDSS

Drain to Gate Voltage (RGS = 20k) (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . VDGR

Gate to Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VGS

Continuous Drain Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .ID

Pulsed Drain Current (Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IDM

Pulsed Avalanche Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . EAS

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PD

Derate Above 25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TJ, TSTG

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s. . . . . . . . . . . . . . . . . . . . . . . . . . . . TL

Package Body for 10s, See Techbrief 334 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Tpkg

RFG50N06LE, RFP50N06LE,

RF1S50N06LESM

60

60

10

50

Refer to Peak Current Curve

Refer to UIS Curve

142

0.95

-55 to 175

UNITS

V

V

V

A

W

W/oC

oC

oC

oC

300

260

CAUTION: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. TJ = 25oC to 150oC.

TC = 25oC, Unless Otherwise Specified

Electrical Specifications

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNITS

Drain to Source Breakdown Voltage

BVDSS

ID = 250A, VGS = 0V, Figure 13

60

Gate Threshold Voltage

VGS(TH)

VGS = VDS, ID = 250A, Figure 12

VDS = 55V, VGS = 0V

VDS = 50V, VGS = 0V, TC = 150oC

250

Zero Gate Voltage Drain Current

IDSS

Gate to Source Leakage Current

IGSS

Drain to Source On Resistance (Note 2)

rDS(ON)

Turn-On Time

tON

Turn-On Delay Time

td(ON)

Rise Time

tr

Turn-Off Delay Time

10

ID = 50A, VGS = 5V, Figure 11

0.022

VDD = 30V, ID = 50A,

RL = 0.6, VGS = 5V,

RGS = 2.5

Figures 10, 18, 19

230

ns

20

ns

170

ns

td(OFF)

48

ns

tf

90

ns

tOFF

165

ns

Fall Time

Turn-Off Time

VGS = 10V

Total Gate Charge

Qg(TOT)

VGS = 0V to 10V

Gate Charge at 5V

Qg(5)

VGS = 0V to 5V

Qg(TH)

VGS = 0V to 1V

Threshold Gate Charge

Input Capacitance

CISS

Output Capacitance

COSS

Reverse Transfer Capacitance

Thermal Resistance Junction to Case

Thermal Resistance Junction to Ambient

RJA

VDD = 48V,

ID = 50A,

RL = 0.96

Figures 21, 21

VDS = 25V, VGS = 0V,

f = 1MHz

Figure 14

96

120

nC

57

70

nC

2.2

2.7

nC

2100

pF

600

pF

CRSS

230

pF

RJC

1.05

oC/W

TO-247

30

oC/W

TO-220AB and TO-263AB

80

oC/W

Source to Drain Diode Specifications

PARAMETER

SYMBOL

Source to Drain Diode Voltage

VSD

Diode Reverse Recovery Time

trr

MIN

TYP

MAX

UNITS

ISD = 45A

TEST CONDITIONS

1.5

ISD = 45A, dISD/dt = 100A/s

125

ns

NOTES:

2. Pulse test: pulse width 80s, duty cycle 2%.

3. Repetitive rating: pulse width limited by Max junction temperature. See Transient Thermal Impedance curve (Figure 3).

RFG50N06LE, RFP50N06LE, RF1S50N06LESM

Unless Otherwise Specified

1.2

60

1.0

50

ID, DRAIN CURRENT (A)

POWER DISSIPATION MULTIPLIER

Typical Performance Curves

0.8

0.6

0.4

0.2

40

30

20

10

0

0

25

50

75

100

150

125

175

25

50

TC , CASE TEMPERATURE (oC)

75

100

125

150

175

TC, CASE TEMPERATURE (oC)

FIGURE 1. NORMALIZED POWER DISSIPATION vs CASE

TEMPERATURE

FIGURE 2. MAXIMUM CONTINUOUS DRAIN CURRENT vs

CASE TEMPERATURE

ZJC, NORMALIZED

THERMAL IMPEDANCE

1

0.5

PDM

0.2

0.1

0.1

t1

t2

0.05

0.02

NOTES:

DUTY FACTOR: D = t1/t2

PEAK TJ = PDM x ZJC x RJC + TC

0.01

SINGLE PULSE

0.01

10-5

10-4

10-3

10-2

10-1

100

101

t, RECTANGULAR PULSE DURATION (s)

FIGURE 3. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCE

TC = 25oC

TJ = MAX RATED

100

100s

1ms

10

10ms

OPERATION IN THIS

AREA MAY BE

LIMITED BY rDS(ON)

1

1

10

100

VDS, DRAIN TO SOURCE VOLTAGE (V)

FIGURE 4. FORWARD BIAS SAFE OPERATING AREA

200

1000

IDM, PEAK CURRENT CAPABILITY (A)

ID, DRAIN CURRENT (A)

500

TC = 25oC

VGS = 10V

VGS = 5V

100

THERMAL IMPEDANCE

MAY LIMIT CURRENT

IN THIS REGION

FOR TEMPERATURES

ABOVE 25oC DERATE PEAK

CURRENT AS FOLLOWS:

175 - TC

I=I

25

10

10-5

10-4

10-3

10-2

150

10-1

100

t, PULSE WIDTH (s)

FIGURE 5. PEAK CURRENT CAPABILITY

101

RFG50N06LE, RFP50N06LE, RF1S50N06LESM

IAS, AVALANCHE CURRENT (A)

300

Unless Otherwise Specified

tAV = (L/R)ln[(IAS*R)/(1.3*RATED BVDSS - VDD) +1]

If R 0

tAV = (L)(IAS)/(1.3*RATED BVDSS - VDD)

If R = 0

100

STARTING TJ = 25oC

10

STARTING TJ = 150oC

(Continued)

100

TC = 25oC

VGS = 4V

75

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

50

VGS = 3V

25

VGS = 2.5V

1

0.01

NOTE:

0.1

1

10

tAV, TIME IN AVALANCHE (ms)

100

1.5

3.0

4.5

VDS, DRAIN TO SOURCE VOLTAGE (V)

VDD = 15V

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

80

-55oC

25oC

ID = 12.5A

175oC

75

50

25

ON RESISTANCE (m)

100

FIGURE 7. SATURATION CHARACTERISTICS

rDS(ON), DRAIN TO SOURCE

IDS(ON), DRAIN TO SOURCE CURRENT (A)

6.0

Refer to Intersil Application Notes AN9321 and AN9322

FIGURE 6. UNCLAMPED INDUCTIVE SWITCHING

1.5

3.0

4.5

VGS, GATE TO SOURCE VOLTAGE (V)

ID = 100A

60

40

ID = 25A

20

0

2.0

6.0

2.5

3.5

3.0

4.0

4.5

5.0

VGS, GATE TO SOURCE VOLTAGE (V)

FIGURE 8. TRANSFER CHARACTERISTICS

FIGURE 9. DRAIN TO SOURCE ON RESISTANCE vs GATE

VOLTAGE AND DRAIN CURRENT

2.5

VDD = 30V, ID = 50A, RL= 0.6

NORMALIZED DRAIN TO SOURCE

ON RESISTANCE

600

tr

500

400

td(OFF)

300

tf

200

td(ON)

100

0

ID = 50A

VDD = 15V

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

0

0

SWITCHING TIME (ns)

VGS = 10V

VGS = 5V

ID, DRAIN CURRENT (A)

Typical Performance Curves

VGS = 5V, ID = 50A

PULSE DURATION = 80s

DUTY CYCLE = 0.5% MAX

2.0

1.5

1.0

0.5

0

10

20

30

40

RGS, GATE TO SOURCE RESISTANCE ()

FIGURE 10. SWITCHING TIME vs GATE RESISTANCE

50

-80

-40

40

80

120

160

TJ, JUNCTION TEMPERATURE (oC)

FIGURE 11. NORMALIZED DRAIN TO SOURCE ON

RESISTANCE vs JUNCTION TEMPERATURE

200

RFG50N06LE, RFP50N06LE, RF1S50N06LESM

Typical Performance Curves

Unless Otherwise Specified

(Continued)

2.0

1.2

1.0

0.5

-40

0

40

80

120

160

TJ, JUNCTION TEMPERATURE (oC)

0.9

0.8

-80

CISS

2000

VGS = 0V, f = 1MHz

CISS = CGS + CGD

CRSS = CGD

COSS CDS + CGD

1000

COSS

500

CRSS

160

0

40

80

120

TJ, JUNCTION TEMPERATURE (oC)

200

5.0

60

VDD = BVDSS

VDD = BVDSS

45

3.75

RL =1.2

IG(REF) = 1.2mA

VGS = 5V

2.5

30

15

PLATEAU VOLTAGES IN

DESCENDING ORDER:

VDD = BVDSS

VDD = 0.75 BVDSS

VDD = 0.50 BVDSS

VDD = 0.25 BVDSS

0

20 ---------------------I G ( ACT )

25

1.25

0

I G ( REF )

0

5

10

15

20

VDS, DRAIN TO SOURCE VOLTAGE (V)

-40

FIGURE 13. NORMALIZED DRAIN TO SOURCE BREAKDOWN

VOLTAGE vs JUNCTION TEMPERATURE

VDS , DRAIN TO SOURCE VOLTAGE (V)

2500

1.0

200

FIGURE 12. NORMALIZED GATE THRESHOLD VOLTAGE vs

JUNCTION TEMPERATURE

1500

1.1

t, TIME (s)

I G ( REF )

80 ---------------------I G ( ACT )

NOTE: Refer to Intersil Application Notes AN7254 and AN7260.

FIGURE 14. CAPACITANCE vs DRAIN TO SOURCE VOLTAGE

FIGURE 15. NORMALIZED SWITCHING WAVEFORMS FOR

CONSTANT GATE CURRENT

Test Circuits and Waveforms

VDS

BVDSS

L

VARY tP TO OBTAIN

REQUIRED PEAK IAS

tP

RG

VDS

IAS

VDD

VDD

-

VGS

DUT

0V

tP

IAS

0

0.01

tAV

FIGURE 16. UNCLAMPED ENERGY TEST CIRCUIT

FIGURE 17. UNCLAMPED ENERGY WAVEFORMS

VGS , GATE TO SOURCE VOLTAGE (V)

1.5

0

-80

C, CAPACITANCE (pF)

ID = 250A

NORMALIZED DRAIN TO SOURCE

BREAKDOWN VOLTAGE

NORMALIZED GATE

THRESHOLD VOLTAGE

VGS = VDS, ID = 250A

RFG50N06LE, RFP50N06LE, RF1S50N06LESM

Test Circuits and Waveforms

(Continued)

tON

tOFF

td(ON)

VDS

td(OFF)

tf

tr

VDS

90%

90%

RL

VGS

DUT

10%

10%

VDD

90%

RGS

VGS

VGS

10%

FIGURE 18. SWITCHING TIME TEST CIRCUIT

50%

50%

PULSE WIDTH

FIGURE 19. RESISTIVE SWITCHING WAVEFORMS

VDS

VDD

RL

Qg(TOT)

VDS

Qg(10) OR Qg(5)

VGS

VDD

VGS

DUT

Ig(REF)

VGS = 2V

0

VGS = 1V FOR

L2 DEVICES

Qg(TH)

VGS = 20V

VGS = 10V FOR

L2 DEVICES

VGS = 10V

VGS = 5V FOR

L2 DEVICES

Ig(REF)

0

FIGURE 20. GATE CHARGE TEST CIRCUIT

FIGURE 21. GATE CHARGE WAVEFORMS

RFG50N06LE, RFP50N06LE, RF1S50N06LESM

PSPICE Electrical Model

SUBCKT 50N06LE 2 1 3 ;

rev 8/11/95

CA 12 8 3.73e-9

CB 15 14 3.73e-9

CIN 6 8 2.08e-9

DBODY 7 5 DBODYMOD

DBREAK 5 11 DBREAKMOD

DPLCAP 10 5 DPLCAPMOD

LDRAIN

DPLCAP

DRAIN

2

10

5

51

ESLC

11

RDRAIN

6

8

EVTHRES

+ 19 8

+

LGATE

GATE

1

EVTEMP

RGATE +

18 22

9

20

21

DBODY

16

MWEAK

MMED

MSTRO

RLGATE

MMED 16 6 8 8 MMEDMOD

MSTRO 16 6 8 8 MSTROMOD

MWEAK 16 21 8 8 MWEAKMOD

+

17

EBREAK 18

50

IT 8 17 1

LSOURCE

CIN

SOURCE

3

7

RSOURCE

RBREAK 17 18 RBREAKMOD 1

RDRAIN 50 16 RDRAINMOD 3.75e-3

RGATE 9 20 1.0

RLDRAIN 2 5 40

RLGATE 1 9 60

RLSOURCE 3 7 30

RSLC1 5 51 RSLCMOD 1e-6

RSLC2 5 50 1e3

RSOURCE 8 7 RSOURCEMOD 6.15e-3

RVTHRES 22 8 RVTHRESMOD 1

RVTEMP 18 19 RVTEMPMOD 1

S1A

S1B

S2A

S2B

DBREAK

RSLC2

ESG

LDRAIN 2 5 4.0e-9

LGATE 1 9 6.0e-9

LSOURCE 3 7 3.0e-9

RLDRAIN

RSLC1

51

EBREAK 11 7 17 18 66.5

EDS 14 8 5 8 1

EGS 13 8 6 8 1

ESG 6 10 6 8 1

EVTHRES 6 21 19 8 1

EVTEMP 20 6 18 22 1

RLSOURCE

S2A

S1A

12

S1B

CA

17

18

RVTEMP

S2B

13

CB

6

8

EGS

19

VBAT

5

8

EDS

IT

14

6 12 13 8 S1AMOD

13 12 13 8 S1BMOD

6 15 14 13 S2AMOD

13 15 14 13 S2BMOD

RBREAK

15

14

13

13

8

+

8

22

RVTHRES

VBAT 22 19 DC 1

ESLC 51 50 VALUE={(V(5,51)/ABS(V(5,51)))*(PWR(V(5,51)/(1e-6*200),4))}

.MODEL DBODYMOD D (IS = 1.70e-12 RS = 3.20e-3 TRS1 = 1.75e-3 TRS2 = 1.75e-6 CJO = 2.55e-9 IKF = 13 XTI = 5.2 TT = 7.00e-8 M = 0.47)

.MODEL DBREAKMOD D (RS = 1.70e-1 IKF = 0.1 TRS1 = 2.00e-3 TRS2 = 8.00e-7)

.MODEL DPLCAPMOD D (CJO = 2.00e-9 IS = 1e-30 VJ = 1.1 M = 0.83 N = 10)

.MODEL MMEDMOD NMOS (VTO = 2.00 KP = 5 IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u RG = 1.0)

.MODEL MSTROMOD NMOS (VTO = 2.42 KP = 128 IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u)

.MODEL MWEAKMOD NMOS (VTO = 1.60 KP = 0.01 IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u RG = 10.0 RS = 0.1)

.MODEL RBREAKMOD RES (TC1 = 1.13e-3 TC2 = 0)

.MODEL RDRAINMOD RES (TC1 = 1.20e-2 TC2 = 6.00e-5)

.MODEL RSLCMOD RES (TC1 = 2.00e-3 TC2 = 1.00e-6)

.MODEL RSOURCEMOD RES (TC1 = 2.00e-3 TC2 =-1.00e-5)

.MODEL RVTHRESMOD RES (TC1 = -2.50e-3 TC2 = -8.50e-6)

.MODEL RVTEMPMOD RES (TC1 = -2.00e-3 TC2 = 5.00e-6)

.MODEL S1AMOD VSWITCH (RON = 1e-5

.MODEL S1BMOD VSWITCH (RON = 1e-5

.MODEL S2AMOD VSWITCH (RON = 1e-5

.MODEL S2BMOD VSWITCH (RON = 1e-5

ROFF = 0.1

ROFF = 0.1

ROFF = 0.1

ROFF = 0.1

VON = -5.3 VOFF= -2.5)

VON = -2.5 VOFF= -5.3)

VON = -1.4 VOFF= 0.5)

VON = 0.5 VOFF= -1.4)

.ENDS

NOTE: For further discussion of the PSPICE model, consult A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global

Temperature Options; IEEE Power Electronics Specialist Conference Records, 1991, written by William J. Hepp and C. Frank Wheatley.

RFG50N06LE, RFP50N06LE, RF1S50N06LESM

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

Sales Office Headquarters

NORTH AMERICA

Intersil Corporation

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (407) 724-7000

FAX: (407) 724-7240

EUROPE

Intersil SA

Mercure Center

100, Rue de la Fusee

1130 Brussels, Belgium

TEL: (32) 2.724.2111

FAX: (32) 2.724.22.05

ASIA

Intersil (Taiwan) Ltd.

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310

FAX: (886) 2 2715 3029

Potrebbero piacerti anche

- Datasheet IRFZ44Documento9 pagineDatasheet IRFZ44henryNessuna valutazione finora

- 93 XX 46Documento28 pagine93 XX 46MohamedElsawiNessuna valutazione finora

- 74HC14DDocumento8 pagine74HC14DmaurosergiorovettaNessuna valutazione finora

- (CHEVROLET) Manual de Taller Chevrolet Spark EVDocumento26 pagine(CHEVROLET) Manual de Taller Chevrolet Spark EVDavid Carlos Dady100% (2)

- PTC Thermistor (Posistor) : Application ManualDocumento14 paginePTC Thermistor (Posistor) : Application ManualhenryNessuna valutazione finora

- Fuel Pump Flow RatesDocumento6 pagineFuel Pump Flow Rateshenry0% (1)

- 200 Circuitos A Transistores PDFDocumento115 pagine200 Circuitos A Transistores PDFElvio Pereyra100% (1)

- 2SC5200 Datasheet en 20160107Documento5 pagine2SC5200 Datasheet en 20160107Hernan Ortiz EnamoradoNessuna valutazione finora

- BC 635Documento4 pagineBC 635Floricica Victor VasileNessuna valutazione finora

- A1271 (To 92)Documento1 paginaA1271 (To 92)Josué GarciaNessuna valutazione finora

- 70 Interesting CircuitsDocumento21 pagine70 Interesting CircuitsHasitha Suneth100% (4)

- B1375Documento2 pagineB1375gordomonayeNessuna valutazione finora

- 2n7000 PDFDocumento7 pagine2n7000 PDFNuraniIndahSNessuna valutazione finora

- A1271 (To 92)Documento1 paginaA1271 (To 92)Josué GarciaNessuna valutazione finora

- B 772Documento6 pagineB 772GlennNessuna valutazione finora

- High Voltage Epitaxial Planar NPN Transistor Technical DataDocumento4 pagineHigh Voltage Epitaxial Planar NPN Transistor Technical DatahenryNessuna valutazione finora

- Uln2001 2004Documento9 pagineUln2001 2004henryNessuna valutazione finora

- TL431ADocumento10 pagineTL431Ad_richard_dNessuna valutazione finora

- ULN200 X ADocumento13 pagineULN200 X AhenryNessuna valutazione finora

- 145Documento12 pagine145henryNessuna valutazione finora

- Mur420 DDocumento8 pagineMur420 DhenryNessuna valutazione finora

- ULN200x, ULQ200x High-Voltage, High-Current Darlington Transistor ArraysDocumento34 pagineULN200x, ULQ200x High-Voltage, High-Current Darlington Transistor ArraysErnesto Alonso González RodríguezNessuna valutazione finora

- Lenovo 3000 C100 Maintenance ManualDocumento90 pagineLenovo 3000 C100 Maintenance ManualarthurkemalNessuna valutazione finora

- 4fpx020-020 Manual MustangDocumento38 pagine4fpx020-020 Manual MustangAdrian_Sktb_8210Nessuna valutazione finora

- Fallas de SensoresDocumento5 pagineFallas de SensoreshenryNessuna valutazione finora

- Falla CKP de ChryslerDocumento2 pagineFalla CKP de ChryslerhenryNessuna valutazione finora

- CKP TRS CPSDocumento10 pagineCKP TRS CPShenryNessuna valutazione finora

- AP-90-12 Web FinalDocumento124 pagineAP-90-12 Web FinalhenryNessuna valutazione finora

- Sensores QuirozDocumento6 pagineSensores QuirozhenryNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Development of Xbloc Concrete Breakwater Armour Units Canada 2003Documento12 pagineDevelopment of Xbloc Concrete Breakwater Armour Units Canada 2003r_anzarNessuna valutazione finora

- CFD Application Tutorials 2Documento35 pagineCFD Application Tutorials 2Jubril AkinwandeNessuna valutazione finora

- MS27069GDocumento7 pagineMS27069Gawesome_600Nessuna valutazione finora

- Power Electronics and Drives Laboratory ManualDocumento71 paginePower Electronics and Drives Laboratory ManualSureshNessuna valutazione finora

- Cazoom Maths. Lines and Angles. Angles On Parallel Lines (A)Documento2 pagineCazoom Maths. Lines and Angles. Angles On Parallel Lines (A)Apex GamingNessuna valutazione finora

- SCIENCE 4 PPT Q3 - Interactive Quiz - Heat, Light, SoundDocumento50 pagineSCIENCE 4 PPT Q3 - Interactive Quiz - Heat, Light, SoundRe ChelNessuna valutazione finora

- Boiler Water ChemistryDocumento63 pagineBoiler Water ChemistryDeepak JayNessuna valutazione finora

- Car crushing hydraulic circuit analysisDocumento22 pagineCar crushing hydraulic circuit analysisphankhoa83100% (1)

- Unit 1 Test ReviewDocumento4 pagineUnit 1 Test Reviewandrew culkinNessuna valutazione finora

- Bullet Holes in PlasticDocumento7 pagineBullet Holes in PlasticSonya PriceNessuna valutazione finora

- 3b4b4f16ac0bcdb8c58665b05a018b4dDocumento8 pagine3b4b4f16ac0bcdb8c58665b05a018b4dWicttor SantosNessuna valutazione finora

- Electrodo de Carbon PDFDocumento2 pagineElectrodo de Carbon PDFAlfredo FloresNessuna valutazione finora

- Package Insert - PYROSPERSE™ Dispersing Agent (English) - Original - 27876Documento7 paginePackage Insert - PYROSPERSE™ Dispersing Agent (English) - Original - 27876Putri DozanNessuna valutazione finora

- Accessible Design LightingDocumento8 pagineAccessible Design LightingArch AmiNessuna valutazione finora

- Year 10 Trigonometry 2Documento4 pagineYear 10 Trigonometry 2Jack LagerNessuna valutazione finora

- GRFCDocumento16 pagineGRFCMako MohamedNessuna valutazione finora

- Engineering Management: Assignment Chapter 8Documento4 pagineEngineering Management: Assignment Chapter 8Aftab AliNessuna valutazione finora

- P1A Data Sheet LetterDocumento7 pagineP1A Data Sheet LetterGovind RaoNessuna valutazione finora

- Civil Engineering: Reinforced Cement Concrete & Pre-Stressed ConcreteDocumento33 pagineCivil Engineering: Reinforced Cement Concrete & Pre-Stressed ConcreteDebendra Dev KhanalNessuna valutazione finora

- Recursion: Fall 2002 CMSC 203 - Discrete Structures 1Documento18 pagineRecursion: Fall 2002 CMSC 203 - Discrete Structures 1Kris BraNessuna valutazione finora

- CBSE Class 12 Chemistry Sample Paper-15: Material Downloaded From - 1 / 14Documento14 pagineCBSE Class 12 Chemistry Sample Paper-15: Material Downloaded From - 1 / 14Allen Neal JonesNessuna valutazione finora

- Dow EmulsifiersDocumento4 pagineDow EmulsifiersxxtupikxxNessuna valutazione finora

- Lesson 3-F5 PhysicsDocumento14 pagineLesson 3-F5 PhysicsCheng WLNessuna valutazione finora

- Gating System Design GuideDocumento11 pagineGating System Design GuideAshok Pradhan100% (1)

- Genetic Algorithms in OptimizationDocumento38 pagineGenetic Algorithms in OptimizationssbhonsaleNessuna valutazione finora

- Center of Mass and The Motion of A SystemDocumento13 pagineCenter of Mass and The Motion of A SystemNitin SharmaNessuna valutazione finora

- Ed081p36 1Documento1 paginaEd081p36 1IHN SisNessuna valutazione finora

- Bidwell 2005Documento6 pagineBidwell 2005Arturo GBNessuna valutazione finora

- POLE FOUNDATION ANALYSISDocumento2 paginePOLE FOUNDATION ANALYSISPrabuVijayNessuna valutazione finora

- Lecture 3Documento10 pagineLecture 3Abhishek SinhaNessuna valutazione finora