Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

KSZ8041NL Eval Board Rev1.1

Caricato da

jmathew_984887Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

KSZ8041NL Eval Board Rev1.1

Caricato da

jmathew_984887Copyright:

Formati disponibili

1

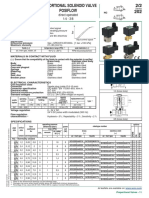

KSZ8041NL Eval Board Revision 1.0

REVISION HISTORY

Table of Contents

DATE

DESCRIPTION

PAGE 01:

PAGE 02:

PAGE 03:

REVISION

1/4/07

Initial Release

1.0

4/27/07

Added 100pF capacitor (C53) on REXT (pin 10) of KSZ8041NL.

1.1

Revision History

KSZ8041NL Board -- Block Diagram

KSZ8041NL Device

CONFIDENTIAL & PROPRIETARY

Title

KSZ8041NL Eval Board

Size

Document Number

Rev

1.1

Revision History

Date:

1

Friday, April 27, 2007

Sheet

5

of

KSZ8041NL EVAL BOARD - BLOCK DIAGRAM

D

3.3V

LDO

5V DC

INPUT

TX / RX pairs

KSZ8041NL

MII / RMII Port Connector

MII / RMII

Signals

10Base-T / 100Base-TX

Integrated Magnetic RJ-45 Jack

25 MHz XTAL

(MII mode)

B

50 MHz REF_CLK from MAC

(RMII mode)

Port Status

LED

Indicators

RESET

Configuration

Headers

CONFIDENTIAL & PROPRIETARY

Title

KSZ8041NL Eval Board

Size

Document Number

Rev

1.1

KSZ8041NL Board -- Block Diagram

Date:

1

Friday, April 27, 2007

Sheet

5

of

3.3V_NL

Notes:

1

2

3

4

SW PUSHBUTTON

C6

10uF

J1

10K

1N4148

+

C4

0.1uF

C3

22uF

CT

3

2

RD+

RX+_NL

CT

RD-

NC

CHS_GND

LED0_NL

LED1_NL

BYP

VIN

GND

EN

+

C5

0.1uF

TP1

R3

C10

0.1uF

C9

10uF

C11

0.1uF

J2

RX-_NL

1

2

3

4

5

6

7

8

RX-_NL

RX+_NL

TX-_NL

TX+_NL

TXD0

TXEN

TXC

INTRP

RXER

RXC

RXDV

VDDIO_3.3

GND

VDDPLL_1.8

VDDA_3.3

RXRX+

TXTX+

XO

24

23

22

21

20

19

18

17

CRS_NL

COL_NL

TXD3_NL

TXD2_NL

TXD1_NL

TXD0_NL

TXEN_NL

TXC_NL

R4

R5

33

33

R6

33

RXER_NL

RXC_NL

RXDV_NL

R7

R8

R9

33

33

33

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

INTRP_NL

C12

49.9

TX+_NL

R11

49.9

TX-_NL

R12

49.9

RX+_NL

49.9

RX-_NL

9

10

11

12

13

14

15

16

XO_NL

R13

C16

22pF

VCC

CRS

COL

TXD3

TXD2

TXD1

TXD0

TX_EN

TX_CLK

TX_ER

RX_ER

RX_CLK

RX_DV

RXD0

RXD1

RXD2

RXD3

MDC

MDIO

VCC

VCC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VCC

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

Male MII Connector

KSZ8041NL

C17

Y1

0.1uF

U1

XI_NL

SIGNAL_GND_NL

MII / RMII Port

3.3V_NL

22pF

25MHz

Place SIGNAL_GND return of C14

close to SIGNAL_GND at 5V input

power to board.

3.3V_NL

XI

REXT

MDIO

MDC

RXD3

RXD2

RXD1

RXD0

R10

C14

C15

0.1uF

C2

47uF

MIC5216-3.3BM5

RST#_NL

CHASSIS_GND_NL

1000pF / 2kV

+5V DC

Power Input

4.7K

TD-

TX-_NL

C13

0.1uF

5V_NL

32

31

30

29

28

27

26

25

TD+

3.3A_NL 1.8VPLL_NL

TX+_NL

10

9

1000pF

100K

3.3V_NL

1

75 75

SHIELD

SHIELD

75 75

C7

0.1uF

RST#

LED1

LED0

CRS

COL

TXD3

TXD2

TXD1

1

2

3

4

5

6

7

8

C1

47uF

C8

10uF

RJ-45

Magnetic Jack

TDK TLA-6T718

OUT

FBEAD

+

S1

+

D1

R1

3.3V_NL

U2

R2

FB1

Push

Button

Reset

3.3A_NL

STEWARD

HI1206N101R-00

3.3A_NL

Power_ON

Reset

1. KSZ8041NL has a Paddle Ground on bottom side of chip.

Refer to datasheet for mechanical dimensions.

2. KSZ8041NL provides the 1.8VPLL supply for VDDPLL_1.8

(pin 2). Decouple 1.8VPLL power rail as shown.

3. Place components (Y1, C16, C17, C53, R14, R15) and (R10,

R11, R12, R13, C13, C15) close to respective pins of U1.

C53

R15

100pF

6.49K

Route both traces of each differential pair

as identical to each other as possible at 6mil

width/6mil parallel spacing, and at least 18

mils away from all other signals.

RXD0_NL

RXD1_NL

RXD2_NL

RXD3_NL

MDC_NL

MDIO_NL

R14

R16

R17

R20

R21

33

33

33

33

TP2

R18

R19

4.7K

NC

TP3

NC

C53 is an additional component to the PCB.

LED Mode

Rework C53 in parallel with R15 (as shown) at

location R15 of PCB.

Strapping Options (Refer to Datasheet for descriptions)

3.3V_NL

RMII Mode (option)

KSZ8041NL

PHY RMII Signals

The RMII signal connections between KSZ8041NL

PHY and external MAC are shown in the table to

the right.

PHYAD0

RXD3_NL

J3

JUMPER

R23

1K

PHYAD1

RXD2_NL

J4

JUMPER

R25

4.7K

PHYAD2

RXD1_NL

J5

JUMPER

R26

4.7K

For RMII mode,

CONFIG0

COL_NL

J6

JUMPER

R27

4.7K

1. Remove crystal circuit (Y1, C16, C17) and TXC

termination (R6).

CONFIG1

CRS_NL

J7

JUMPER

R28

4.7K

CONFIG2

RXDV_NL

J8

JUMPER

R29

4.7K

ISO

RXER_NL

J9

JUMPER

R30

4.7K

NWAYEN

LED0_NL

J10

JUMPER

R31

1K

SPEED

LED1_NL

J11

JUMPER

R32

1K

DUPLEX

RXD0_NL

J12

JUMPER

R33

1K

2. Populate R14 with 0 Ohm and R19 with 33 Ohm

to connect 50MHz Reference Clock (provided by

MAC side via J2 pin 12) to U1 pin 9 (XI input).

3. Select RMII mode by setting strapping pins

CONFIG[2:0] to '001'.

4. Connect J2 (RMII Port) to board with RMII MAC

(e.g. Micrel KSZ8893MQL Eval Board).

KSZ8893MQL

MAC RMII Signals

[01]

LED0

LINK/ACT

LINK

LED1

SPEED

ACT

3.3V_NL

LED1

Name

Pin #

Type

Name

Type

REFCLK

Input

REF_CLK

Input

TX_EN

23

Input

CRS_DV

Output

TXD[1]

25

Input

RXD[1]

Output

TXD[0]

24

Input

RXD[0]

Output

CRSDV

18

Output

TX_EN

Input

RXD[1]

15

Output

TXD[1]

Input

RXD[0]

16

Output

TXD[0]

Input

Title

RX_ER

20

Output

TX_ER

Input

Size

R22

220

LED0_NL

R24

220

LED1_NL

LEDx2

CONFIDENTIAL & PROPRIETARY

KSZ8041NL Eval Board

Document Number

Rev

1.1

KSZ8041NL Device

Date:

[00]

Friday, April 27, 2007

Sheet

5

of

Potrebbero piacerti anche

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionDa EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNessuna valutazione finora

- P44x Enco E33Documento14 pagineP44x Enco E33Dongro MalNessuna valutazione finora

- Pioneer Deh 340, Deh 34, Deh 3400Documento37 paginePioneer Deh 340, Deh 34, Deh 3400Dan GuertinNessuna valutazione finora

- Sony cfd-v10 SMDocumento50 pagineSony cfd-v10 SMFerran AlfonsoNessuna valutazione finora

- CA12000202-A Pump Starter With ProfibusDocumento1 paginaCA12000202-A Pump Starter With Profibusnickname12345Nessuna valutazione finora

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Da EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Valutazione: 4.5 su 5 stelle4.5/5 (3)

- Service Manual: Video Camera RecorderDocumento19 pagineService Manual: Video Camera RecorderFilmfoto FilmfotoatyahoocomNessuna valutazione finora

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysDa EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNessuna valutazione finora

- 32HFL4441D27Documento126 pagine32HFL4441D27Jim HarmkeNessuna valutazione finora

- Ax-7 Service NotesDocumento17 pagineAx-7 Service NotesChristopher A ArcherNessuna valutazione finora

- 60528Documento23 pagine60528Andres CaminoNessuna valutazione finora

- 3Y11 FullDocumento24 pagine3Y11 FulltodorloncarskiNessuna valutazione finora

- BLW60C CNV 2Documento15 pagineBLW60C CNV 2myfarlockNessuna valutazione finora

- C&I Cable Schedule - 090710 E-12 PDFDocumento139 pagineC&I Cable Schedule - 090710 E-12 PDFAnonymous vcadX45TD7Nessuna valutazione finora

- Acer Aspire 3610 - Wistron Morar - Rev SBDocumento40 pagineAcer Aspire 3610 - Wistron Morar - Rev SBPer JensenNessuna valutazione finora

- C&S Switchgear Prices 10-6-13Documento42 pagineC&S Switchgear Prices 10-6-13bhaveshbhoi75% (4)

- CLF1G0060 10 - 1G0060S 10Documento18 pagineCLF1G0060 10 - 1G0060S 10Narasimha SunchuNessuna valutazione finora

- Forbid Permit SS B1 B2 Forbid Permit ValsDocumento3 pagineForbid Permit SS B1 B2 Forbid Permit ValsjosephrobinNessuna valutazione finora

- 01-02-10 100baset CPU Conn Box Cable-02Documento6 pagine01-02-10 100baset CPU Conn Box Cable-02maverick11Nessuna valutazione finora

- Sony Aa CDX-CA680X CDX-L580XDocumento8 pagineSony Aa CDX-CA680X CDX-L580XБорис ДидорукNessuna valutazione finora

- Brother PT-1250 C, CC, LB, Lbf1 Parts ManualDocumento18 pagineBrother PT-1250 C, CC, LB, Lbf1 Parts ManualDuplessisNessuna valutazione finora

- Pioneer Deh-P770mp, Deh-P7700mp, Deh-P7750mp Service ManualDocumento19 paginePioneer Deh-P770mp, Deh-P7700mp, Deh-P7750mp Service ManualOssian Valera PinedaNessuna valutazione finora

- KW W900 2011 PDFDocumento4 pagineKW W900 2011 PDFLulu Cordova100% (1)

- Indent No. Annexure - 1 Technical Specification of Alstom / Areva/ Make Protection Relay With Case. 1. CDG31 As Below Specs 4 NosDocumento7 pagineIndent No. Annexure - 1 Technical Specification of Alstom / Areva/ Make Protection Relay With Case. 1. CDG31 As Below Specs 4 NosYaseen SagarNessuna valutazione finora

- GT I9505 Tshoo 7 PDFDocumento132 pagineGT I9505 Tshoo 7 PDFAlvaro Eduardo Chaparro Giron0% (1)

- 80H1032350xA0 6G 24 Port Dual Domain SAS Expander Backplane User Manual - 20120413Documento10 pagine80H1032350xA0 6G 24 Port Dual Domain SAS Expander Backplane User Manual - 20120413BradWaiteNessuna valutazione finora

- Avr400 Service ManualDocumento34 pagineAvr400 Service ManualwatteaucarNessuna valutazione finora

- Air ConditionerDocumento74 pagineAir Conditionermuzaaj100% (1)

- 74LS107 EtcDocumento6 pagine74LS107 EtcBagus Tri Syahputra IINessuna valutazione finora

- Philips 40pfl6606h 12 Chassis q552 2e La SM PDFDocumento114 paginePhilips 40pfl6606h 12 Chassis q552 2e La SM PDFTestrooteNessuna valutazione finora

- Sony XR 5w497rbDocumento14 pagineSony XR 5w497rbwlodexNessuna valutazione finora

- ARP3247Documento14 pagineARP3247Norman TranNessuna valutazione finora

- Inter M Pt-9107sDocumento16 pagineInter M Pt-9107sspeedyeduNessuna valutazione finora

- Pioneer A-109 SchematicDocumento3 paginePioneer A-109 SchematicJohn OxleyNessuna valutazione finora

- PDP-5050SX: Plasma DisplayDocumento3 paginePDP-5050SX: Plasma DisplayatvstereoNessuna valutazione finora

- Service Manual: CDX-L480XDocumento20 pagineService Manual: CDX-L480Xkeremelekika7Nessuna valutazione finora

- Delta Dac-19m008 Tea1532 Oz964 Dac12m035Documento55 pagineDelta Dac-19m008 Tea1532 Oz964 Dac12m035Carlos A. TorresNessuna valutazione finora

- Ecs V10il1 - 37GV10000-C0 - Rev CDocumento32 pagineEcs V10il1 - 37GV10000-C0 - Rev CHendra R. Rattu75% (4)

- BK4811B Datasheet V1.2Documento37 pagineBK4811B Datasheet V1.2BradMorse50% (2)

- RX2 Design DocumentationDocumento8 pagineRX2 Design DocumentationAbhiram KplyNessuna valutazione finora

- Pic 16 F 628Documento20 paginePic 16 F 628Merényi Oszkár100% (1)

- Service Manual: Fm/Am Compact Disc PlayerDocumento10 pagineService Manual: Fm/Am Compact Disc PlayerelekossNessuna valutazione finora

- 01 132 11kv TransformerDocumento76 pagine01 132 11kv TransformerLauren Norris100% (1)

- Autoestereo Pioneer DEH-4090MP DEH-6010MPDocumento39 pagineAutoestereo Pioneer DEH-4090MP DEH-6010MPGustavo De la ONessuna valutazione finora

- Samsung, PS42V4SX-XEU - D65CP ChassisDocumento39 pagineSamsung, PS42V4SX-XEU - D65CP ChassisVincent StanleyNessuna valutazione finora

- Service Manual: FM/MW/LW Compact Disc PlayerDocumento12 pagineService Manual: FM/MW/LW Compact Disc PlayerTiago MouraNessuna valutazione finora

- q45 - rampAPPLE 台式G5线路图.bakDocumento74 pagineq45 - rampAPPLE 台式G5线路图.bakmarkbillupsNessuna valutazione finora

- GT Relay PanelDocumento53 pagineGT Relay PanelPamela Bradley100% (1)

- Tda 4662Documento12 pagineTda 4662Miguel TorresNessuna valutazione finora

- 32 PFL 340477Documento67 pagine32 PFL 340477Anonymous Gj5yPUC2JNessuna valutazione finora

- BLF6G22-180PN 2Documento11 pagineBLF6G22-180PN 2mihai315300100% (1)

- Mainboard Foxconn Model-865a01Documento44 pagineMainboard Foxconn Model-865a01Nicu LiviuNessuna valutazione finora

- 7-1 Overall Block DiagramDocumento4 pagine7-1 Overall Block DiagramCraig KalinowskiNessuna valutazione finora

- Philips Chassis Tpm5.2e-LaDocumento59 paginePhilips Chassis Tpm5.2e-Larolandas1970Nessuna valutazione finora

- Dell Inspiron 1440 - Wistron ALBA UMADocumento61 pagineDell Inspiron 1440 - Wistron ALBA UMACao Bồi Nông ThônNessuna valutazione finora

- SLD of 6.6kV Unit Board 7UADocumento10 pagineSLD of 6.6kV Unit Board 7UAVenkatesh RaoNessuna valutazione finora

- FTM 181 Manual Rev 3Documento3 pagineFTM 181 Manual Rev 3Brandi ChandlerNessuna valutazione finora

- Onvif Interface Guide Specification: January 2019Documento15 pagineOnvif Interface Guide Specification: January 2019jmathew_984887Nessuna valutazione finora

- ONVIF Imaging Service SpecDocumento16 pagineONVIF Imaging Service Specjmathew_984887Nessuna valutazione finora

- ONVIF Profile Policy v2-0Documento30 pagineONVIF Profile Policy v2-0jmathew_984887Nessuna valutazione finora

- BibTeX - WikiDocumento7 pagineBibTeX - Wikijmathew_984887Nessuna valutazione finora

- Asco Express GuideDocumento34 pagineAsco Express Guidejmathew_984887Nessuna valutazione finora

- Labview & Labview NXGDocumento4 pagineLabview & Labview NXGjmathew_984887Nessuna valutazione finora

- ASCO Solenoid ValvesDocumento2 pagineASCO Solenoid Valvesjmathew_984887Nessuna valutazione finora

- Features: EconolineDocumento2 pagineFeatures: Econolinejmathew_984887Nessuna valutazione finora

- SDR Lead User Handbook 3rdedition US LTR WR2Documento28 pagineSDR Lead User Handbook 3rdedition US LTR WR2omegavnNessuna valutazione finora

- EMI Notes For ElectronicsDocumento2 pagineEMI Notes For Electronicsjmathew_984887Nessuna valutazione finora

- DevCon 07 5 E Proof 2015-11-19 PDFDocumento923 pagineDevCon 07 5 E Proof 2015-11-19 PDFjmathew_984887Nessuna valutazione finora

- Before DaVinciDocumento60 pagineBefore DaVincijmathew_984887Nessuna valutazione finora

- Microwind Design FlowDocumento1 paginaMicrowind Design Flowjmathew_984887Nessuna valutazione finora

- Sahara 120 FVO OvenDocumento3 pagineSahara 120 FVO Ovenjmathew_984887Nessuna valutazione finora

- NCP349 Positive Overvoltage Protection Controller With Internal Low R Nmos FetDocumento12 pagineNCP349 Positive Overvoltage Protection Controller With Internal Low R Nmos Fetjmathew_984887Nessuna valutazione finora

- KSZ8041NL: General DescriptionDocumento45 pagineKSZ8041NL: General Descriptionjmathew_984887Nessuna valutazione finora

- BSNL Codes UpdatedDocumento44 pagineBSNL Codes Updatedjmathew_984887Nessuna valutazione finora

- Beamex MC6 Brochure ENGDocumento20 pagineBeamex MC6 Brochure ENGjmathew_984887Nessuna valutazione finora

- MCP2510 To MCP2515Documento6 pagineMCP2510 To MCP2515jmathew_984887100% (1)

- Resistance Weld Thru-Hole Crystal: Features OptionsDocumento1 paginaResistance Weld Thru-Hole Crystal: Features Optionsjmathew_984887Nessuna valutazione finora

- Soldier Systems 123A tcm26-22011 PDFDocumento20 pagineSoldier Systems 123A tcm26-22011 PDFHumberto Trevellin100% (3)

- Marshall Class 5 ManualDocumento4 pagineMarshall Class 5 ManualDioy PalloneNessuna valutazione finora

- Optimization of The Crest Factor For Complex-ValueDocumento9 pagineOptimization of The Crest Factor For Complex-Valuegahopa1479Nessuna valutazione finora

- Eel 3123Documento31 pagineEel 3123Thusith WijayawardenaNessuna valutazione finora

- Psi 500I Documents: Product Document No. RevisionDocumento30 paginePsi 500I Documents: Product Document No. RevisionWildemar VelosoNessuna valutazione finora

- Higher - O-O-O-Emf - O-O-O - Past Paper Questions 2000 - 2010Documento10 pagineHigher - O-O-O-Emf - O-O-O - Past Paper Questions 2000 - 2010Murray PhysicsNessuna valutazione finora

- Max-Ng Overview and NGN ServicesDocumento33 pagineMax-Ng Overview and NGN ServicessatyaNessuna valutazione finora

- Ibm - R61i Vga ShareDocumento100 pagineIbm - R61i Vga Shareحسن علي نوفلNessuna valutazione finora

- Project Titles in Mobile Ad Hoc NetworksDocumento3 pagineProject Titles in Mobile Ad Hoc NetworkssrkmattaNessuna valutazione finora

- ECE Board Exam SyllabiDocumento57 pagineECE Board Exam SyllabilesterPECENessuna valutazione finora

- 2019 - JSS - A Hybrid Structure Dual Path Step Down Converter With 96.2 Peak Efficiency Using 250mohm DCR InductorDocumento9 pagine2019 - JSS - A Hybrid Structure Dual Path Step Down Converter With 96.2 Peak Efficiency Using 250mohm DCR Inductor王睿琛Nessuna valutazione finora

- Lab-4: DC Bridges: 1. ObjectiveDocumento12 pagineLab-4: DC Bridges: 1. ObjectiveAsad RazaNessuna valutazione finora

- Beken BK3633Documento26 pagineBeken BK3633AlexandrNessuna valutazione finora

- Sentry MultistandardDocumento8 pagineSentry MultistandardDragos ComanNessuna valutazione finora

- 6.012 DP: CMOS Integrated Differential Amplifier: Tony Hyun KimDocumento9 pagine6.012 DP: CMOS Integrated Differential Amplifier: Tony Hyun Kimanil kumarNessuna valutazione finora

- Intro To Industrial Process Control SystemsDocumento24 pagineIntro To Industrial Process Control Systemsmuhammad izzulNessuna valutazione finora

- AOZ5507QI Support DocumentsDocumento17 pagineAOZ5507QI Support DocumentsNorberto CruzNessuna valutazione finora

- Load Line and Q-PointDocumento3 pagineLoad Line and Q-PointRavi Kanth M NNessuna valutazione finora

- Astm A772 PDFDocumento4 pagineAstm A772 PDFCristian OtivoNessuna valutazione finora

- Extracted Pages From ATV900 - Programming - Manual - EN - NHA80757 - 05Documento2 pagineExtracted Pages From ATV900 - Programming - Manual - EN - NHA80757 - 05Goran MladenovicNessuna valutazione finora

- SPC232SF SPmodeDocumento15 pagineSPC232SF SPmodeHelder CostaNessuna valutazione finora

- Wireless Communication Lecture Notes by Dr.O.Cyril Mathew, PHD., Al-Ameen Engineering College-ErodeDocumento76 pagineWireless Communication Lecture Notes by Dr.O.Cyril Mathew, PHD., Al-Ameen Engineering College-ErodeCyril Mathew0% (1)

- Loru SBR Rakha KarDocumento9 pagineLoru SBR Rakha KarPython SolutionsNessuna valutazione finora

- Phoenix Contact - Relay Module - Rif-0-Rpt-24dc - 1 - 2903361Documento5 paginePhoenix Contact - Relay Module - Rif-0-Rpt-24dc - 1 - 2903361alexender2kNessuna valutazione finora

- Lab ManualDocumento29 pagineLab ManualAnantharam RaoNessuna valutazione finora

- 929midterm Exam Routine SP 23 and Au 2022Documento1 pagina929midterm Exam Routine SP 23 and Au 2022ET201004 Md Imam HossainNessuna valutazione finora

- 3.7 Digital Input Module SM 321 DI 32 X DC 24 V (6ES7321-1BL00-0AA0)Documento3 pagine3.7 Digital Input Module SM 321 DI 32 X DC 24 V (6ES7321-1BL00-0AA0)LanreSKNessuna valutazione finora

- Parasound HCA 1200Documento8 pagineParasound HCA 1200theaNessuna valutazione finora

- Electronic Parts Symbols Labeling and ApplicationDocumento23 pagineElectronic Parts Symbols Labeling and ApplicationRonald ConstantinoNessuna valutazione finora