Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

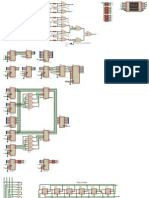

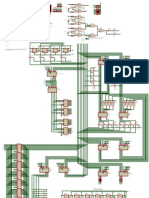

SAP-1 Simple As Possible Microprocessor - Original Design

Caricato da

Farhan S. Adul100%(1)Il 100% ha trovato utile questo documento (1 voto)

205 visualizzazioni1 paginaTitolo originale

SAP-1 Simple As Possible Microprocessor - Original Design.docx

Copyright

© © All Rights Reserved

Formati disponibili

DOCX, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOCX, PDF, TXT o leggi online su Scribd

100%(1)Il 100% ha trovato utile questo documento (1 voto)

205 visualizzazioni1 paginaSAP-1 Simple As Possible Microprocessor - Original Design

Caricato da

Farhan S. AdulCopyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOCX, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 1

Note: The RAM has inverting outputs so this switch

has also been inverted to enter the correct data.

UP = Logic 0 input = Logic 1 Output fromRAM

DOWN = Logic 1 input = Logic 0 output fromRAM

(Observe W-Bus indicators for correct value)

Note: This extra switch was added to

isolate the output of the Program Counter

fromthe W-bus when entering data, otherwise

a logic contention will occur.

Note: The 555 timer circuit has been substituted with

a virtual clock source to speed up the simulation.

Memory Address Register

Note: These pull-up resistors are necessary

because t he out put s of t he 74LS89 ( substi t ute

for the 74LS189) are open collector.

Ring Counter

Instruction Decoder Control Matrix

C

p

E

p

L

m

C

E

L

i

E

i

L

a

E

a

S

u

E

u

L

b

L

o

T

1

T

2

T

3

T

4

T

5

T

6

J

1

Q

3

CLK

12

K

4

Q

2

R

1

3

U36:A

74LS107

J

8

Q

5

CLK

9

K

11

Q

6

R

1

0

U36:B

74LS107

J

1

Q

3

CLK

12

K

4

Q

2

R

1

3

U38:A

74LS107

J

8

Q

5

CLK

9

K

11

Q

6

R

1

0

U38:B

74LS107

J

1

Q

3

CLK

12

K

4

Q

2

R

1

3

U37:A

74LS107

J

8

Q

5

CLK

9

K

11

Q

6

R

1

0

U37:B

74LS107

T6

T5

T4

T3

T2

T1

1 2

U31:A

3 4

U31:B

5 6

U31:C

13 12

U31:D

CLK

CLR

1

2

4

5

6

U32:A

9

10

12

13

8

U32:B

1

2

4

5

6

U33:A

9

10

12

13

8

U33:B

1

2

4

5

6

U34:A

1

1

1

0

U35:E

1

3

1

2

U35:D

1 2

U35:A

3 4

U35:B

5 6

U35:C

9 8

U35:F

HLT

1

2

3

4

5

6

1

0

9

8

1

3

1

2

1

1

1

2

4

5

6

U44:A

Cp Ep

1

2

U47:A

Lm

U39:D

1

2

3

4

5

6

1

0

9

8

1

3

1

2

1

1

U40:D

1

2

3

4

5

6

1

0

9

8

1

3

1

2

1

1

U41:D

1

2

3

4

5

6

1

0

9

8

1

3

1

2

1

1

U42:D

1

2

3

4

5

6

1

0

9

8

U43:C

9

1

0

1

2

1

3

8

U44:B

1

2

1

3

1

2

U45:A

3

4

5

6

U45:B

1

2

3

U46:A

4

5

6

U46:B

3

4

U47:B

5

6

U47:C

9

8

U47:F

1

1

1

0

U47:E

1

3

1

2

U47:D

1

2

U48:A

3

4

U48:B

CE Li Ei La Ea S u Eu Lb Lo

LDA

ADD

SUB

OUT

1

2

13

12

U25:A

CLR

CLR

SW5 START

CLEAR

SW6

Clear/St art

Si ngl e Step

LOW

HIGH

SW7

Manual/ Auto

Manual

Aut o

HLT

13

12

11

U26:D

CLK

CLK

1 2

U27:A

3 4

U27:B

5 6

U27:C

1

2

3

U24:A

4

5

6

U24:B

7400

10

9

8

U24:C

13

12

11

U24:D

7400

VCC

VCC

VCC

U25:B(C)

INIT=LOW

START=0

COUNT=-1

CLOCK=1

4

5

6

U26:B

1

2

3

U26:A

VCC

VCC

VCC

3

4

5

6

U25:B

HLT

I7 I6 I5 I4

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

J

1

Q

3

CLK

12

K

4

Q

2

R

1

3

U1:A

74LS107

J

8

Q

5

CLK

9

K

11

Q

6

R

1

0

U1:B

74LS107

J

1

Q

3

CLK

12

K

4

Q

2

R

1

3

U2:A

74LS107

J

8

Q

5

CLK

9

K

11

Q

6

R

1

0

U2:B

74LS107

2

3

1

U3:A

5

6

4

U3:B

9

8

10

U3:C

1

2

1

1

13

U3:D

74LS126

Cp

CLK

CLR

ENpc

D

0

1

4

Q

0

3

D

1

1

3

Q

1

4

D

2

1

2

Q

2

5

D

3

1

1

Q

3

6

C

L

K

7

O

E

1

1

O

E

2

E

1

E

2

2

9

1

0

M

R

1

5

U4

74LS173

1

A

2

1

Y

4

1

B

3

2

A

5

2

Y

7

2

B

6

3

A

1

1

3

Y

9

3

B

1

0

4

A

1

4

4

Y

1

2

4

B

1

3

A

/ B

E

1

1

5

U5

74LS157

2-1 Multiplexer

CLK

Lm

W4 W3 W2 W1 W0 W5 W6 W7

ENmar

ADR3

ADR2

ADR1

ADR0

D

1

4

D

2

6

D

3

1

0

D

4

1

2

A

2

1

4

A

3

1

3

M

E

2

W

E

3

Q

1

5

Q

2

7

Q

3

9

Q

4

1

1

A

0

1

A

1

1

5

U6

74LS89

16 X 4-bit RAM

D

1

4

D

2

6

D

3

1

0

D

4

1

2

A

2

1

4

A

3

1

3

M

E

2

W

E

3

Q

1

5

Q

2

7

Q

3

9

Q

4

1

1

A

0

1

A

1

1

5

U7

74LS89

16 X 4-bit RAM

D4

D5

D6

D7

D0

D1

D2

D3

WEr am

ENram

WEr am

ENram

D

0

1

4

Q

0

3

D

1

1

3

Q

1

4

D

2

1

2

Q

2

5

D

3

1

1

Q

3

6

C

L

K

7

O

E

1

1

O

E

2

E

1

E

2

2

9

1

0

M

R

1

5

U8

74LS173

Instruction

Regi st er

( OPCode)

D

0

1

4

Q

0

3

D

1

1

3

Q

1

4

D

2

1

2

Q

2

5

D

3

1

1

Q

3

6

C

L

K

7

O

E

1

1

O

E

2

E

1

E

2

2

9

1

0

M

R

1

5

U9

74LS173

Instruction

Regi st er

( Address)

CLK CLK

Ei

Li

Li

CLR

I 7

I 6

I 5

I 4

VCC

D

0

1

4

Q

0

3

D

1

1

3

Q

1

4

D

2

1

2

Q

2

5

D

3

1

1

Q

3

6

C

L

K

7

O

E

1

1

O

E

2

2

E

1

9

E

2

1

0

M

R

U11

74LS173

Accumul ator

D

0

1

4

Q

0

3

D

1

1

3

Q

1

4

D

2

1

2

Q

2

5

D

3

1

1

Q

3

6

C

L

K

7

O

E

1

1

O

E

2

2

E

1

9

E

2

1

0

M

R

U10

74LS173

Accumul ator

2 3

1

5 6

4

9 8

1

0

12 11

1

3

U12:D

74LS126

Accumul ator

Out put

2 3

1

5 6

4

9 8

1

0

12 11

1

3

U13:D

74LS126

Accumul ator

Out put

Ea

A

0

5

A

1

3

A

2

1

4

A

3

1

2

B

0

6

B

1

2

B

2

1

5

B

3

1

1

C

0

7

C

4

9

S

0

4

S

1

1

S

2

1

3

S

3

1

0

U16

74LS283

Full Adder

(MSB)

A

0

5

A

1

3

A

2

1

4

A

3

1

2

B

0

6

B

1

2

B

2

1

5

B

3

1

1

C

0

7

C

4

9

S

0

4

S

1

1

S

2

1

3

S

3

1

0

U17

74LS283

Full Adder

(LSB)

1

5

1

5

La

CLK

La

CLK

Ea

1

2

3

4

5

6

9

8

1

2

1

1

U15:D

74LS86

1

2

3

4

5

6

9

8

1

2

1

1

U14:D

74LS86

S u Carry

1

0

S u

1

3

S u

1

3

1

0

1

2

1

1

13

U19:D

74LS126

9

8

10

5

6

4

2

3

1

1

2

1

1

13

U18:D

74LS126

9

8

10

5

6

4

2

3

1

Carry

D

0

1

4

Q

0

3

D

1

1

3

Q

1

4

D

2

1

2

Q

2

5

D

3

1

1

Q

3

6

C

L

K

7

O

E

1

1

O

E

2

2

E

1

9

E

2

1

0

M

R

U20

74LS173

B Regi st er

(MSB)

D

0

1

4

Q

0

3

D

1

1

3

Q

1

4

D

2

1

2

Q

2

5

D

3

1

1

Q

3

6

C

L

K

7

O

E

1

1

O

E

2

2

E

1

9

E

2

1

0

M

R

U21

74LS173

B Regi st er

(LSB)

D

0

1

4

Q

0

3

D

1

1

3

Q

1

4

D

2

1

2

Q

2

5

D

3

1

1

Q

3

6

C

L

K

7

O

E

1

1

O

E

2

2

E

1

9

E

2

1

0

M

R

1

5

U22

74LS173

Out put Regi st er

D

0

1

4

Q

0

3

D

1

1

3

Q

1

4

D

2

1

2

Q

2

5

D

3

1

1

Q

3

6

C

L

K

7

O

E

1

1

O

E

2

2

E

1

9

E

2

1

0

M

R

1

5

U23

74LS173

Out put Regi st er

CLK

Lo

CLK

Lo

Lb

CLK

1

5

Lb

CLK

1

5

O

P

0

O

P

1

O

P

2

O

P

3

O

P

4

O

P

5

O

P

6

O

P

7

A

D

R

3

A

D

R

2

A

D

R

1

A

D

R

0

SW2

Progr am/ Run

VCC

CE

ENram

ENmar

O

N

O

F

F

4

8

7

6

5

SW1

Address

Swit ch

O

F

F

O

N

9

SW3

OPCode / Dat a

Swi t ches

D

7

8

D

6

7

D

5

6

D

4

5

D

3

4

D

2

3

D

1

2

1

D

0

SW4

Write

Memory

VCC

WEr am

W

7

W

6

W

5

W

4

W

3

W

2

W

1

W

0

?

?

?

?

?

?

?

?

O

P

0

O

P

1

O

P

2

O

P

3

O

P

4

O

P

5

O

P

6

O

P

7

1

2

3

SW8

Progr am/ Run

ENpc

Ep

Eu

1

6

1

5

1

4

1

3

1

2

1

1

1

0

ADR3

ADR2

ADR1

ADR0

D7

D6

D5

D4

D3

D2

D1

D0

VCC

CLR CLR

Potrebbero piacerti anche

- Informatica ProjectDocumento4 pagineInformatica Projectshivarajmy100% (2)

- SAP-1 Simple As Possible Computer Schematic DiagramDocumento1 paginaSAP-1 Simple As Possible Computer Schematic Diagrampong74ls100% (5)

- Sap 2Documento35 pagineSap 2Michael Vincent B. Nierva88% (8)

- 16 Bit CalculatorDocumento17 pagine16 Bit CalculatorPankaj JaiswalNessuna valutazione finora

- SAP-1 Simple As Possible Computer Schematic Diagram - Updated DesignDocumento1 paginaSAP-1 Simple As Possible Computer Schematic Diagram - Updated Designpong74lsNessuna valutazione finora

- ASAP-2 Almost Simple As Possible Computer SchematicDocumento1 paginaASAP-2 Almost Simple As Possible Computer Schematicpong74lsNessuna valutazione finora

- SAP-1 Simple As Possible Computer With Microcoded ROMDocumento1 paginaSAP-1 Simple As Possible Computer With Microcoded ROMpong74lsNessuna valutazione finora

- SAP-1 Simple As Possible Computer With Discrete Component RAMDocumento1 paginaSAP-1 Simple As Possible Computer With Discrete Component RAMpong74lsNessuna valutazione finora

- Sap 3 ArchitectureDocumento5 pagineSap 3 ArchitectureYzza Veah Esquivel100% (3)

- PLMU Computer Studies Dept SAP-1 modificationDocumento17 paginePLMU Computer Studies Dept SAP-1 modificationJaysen GeronimoNessuna valutazione finora

- Sap 1 2Documento21 pagineSap 1 2Brandon Maciel50% (2)

- SCH CpuDocumento1 paginaSCH CpuWilliams Giorgio Sicsu100% (2)

- MicroprocessorDocumento2 pagineMicroprocessorKiran TimsinaNessuna valutazione finora

- Sap 1 Manual NewDocumento41 pagineSap 1 Manual NewAlexis John Rubio0% (1)

- 4) PIC IO Port ProgrammingDocumento18 pagine4) PIC IO Port ProgrammingArryshah Dahmia100% (2)

- Engineering-Circuit-Analysis-Solutions-7ed-Hayt - (Upload by R1LhER PDFDocumento385 pagineEngineering-Circuit-Analysis-Solutions-7ed-Hayt - (Upload by R1LhER PDFFernandoFerP.R0% (4)

- Z80 IsDocumento16 pagineZ80 IsDang KhueNessuna valutazione finora

- Bueno - DSN 06/05/2012 F:/bueno - DSN: File Name: DateDocumento1 paginaBueno - DSN 06/05/2012 F:/bueno - DSN: File Name: DateOswaldo LucioNessuna valutazione finora

- 6Q7 9Q8 1 1 Q9 1 2 Q 5 - 9 1Gnd 2Trg 3out 4Rst5Ctl 6Thr 7dis 8VccDocumento4 pagine6Q7 9Q8 1 1 Q9 1 2 Q 5 - 9 1Gnd 2Trg 3out 4Rst5Ctl 6Thr 7dis 8VccAlexon DomingoNessuna valutazione finora

- ATmega8-L Microcontroller Circuit DiagramDocumento3 pagineATmega8-L Microcontroller Circuit DiagramNguyễn Văn HinhNessuna valutazione finora

- Driver StepDocumento1 paginaDriver StepTam Phuong NguyenNessuna valutazione finora

- Schematic Diagrams Appendix BDocumento0 pagineSchematic Diagrams Appendix BfclodoaldoNessuna valutazione finora

- 16 AUV Motor ControllerDocumento1 pagina16 AUV Motor ControllerGhazal IraniNessuna valutazione finora

- D C B A: BipolarDocumento4 pagineD C B A: Bipolarjurandir21Nessuna valutazione finora

- CPU Board Logic Diagram System 6 PinballDocumento0 pagineCPU Board Logic Diagram System 6 PinballMauricio RaúlNessuna valutazione finora

- DOP7Documento2 pagineDOP7Nghia Do100% (1)

- Computer-Generated Circuit DiagramDocumento1 paginaComputer-Generated Circuit Diagramatomo33Nessuna valutazione finora

- Z80 computer circuit diagram with component list and notesDocumento1 paginaZ80 computer circuit diagram with component list and notesmjs6029100% (1)

- Sony Vaio Mbx-126 - Quanta Je5.1Documento36 pagineSony Vaio Mbx-126 - Quanta Je5.1nunoq171Nessuna valutazione finora

- SCH UnipolarDocumento1 paginaSCH UnipolarSerchu_29Nessuna valutazione finora

- Sony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICDocumento36 pagineSony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICvideoson0% (1)

- GPL32200A EMUBOARD SchematicDocumento9 pagineGPL32200A EMUBOARD SchematicFrancis TaisantNessuna valutazione finora

- GT S5360Documento51 pagineGT S5360radiobrunoNessuna valutazione finora

- Gc150ata 01Documento5 pagineGc150ata 01ValdairVelozoSoaresNessuna valutazione finora

- Compact title for circuit diagram documentDocumento3 pagineCompact title for circuit diagram documentAdrian PeterNessuna valutazione finora

- Tecv1 01Documento1 paginaTecv1 01Ana Claudia BarbosaNessuna valutazione finora

- 8 Sensors Circuit DiagramDocumento6 pagine8 Sensors Circuit DiagramtrngocluanNessuna valutazione finora

- Daewoo DVG 6000DDocumento12 pagineDaewoo DVG 6000DOssian Valera PinedaNessuna valutazione finora

- PR D Q: Control Input Pin 1 - Direction Pin 3 - Step Pulses Pin 5 - Motor On/Off (0 On)Documento1 paginaPR D Q: Control Input Pin 1 - Direction Pin 3 - Step Pulses Pin 5 - Motor On/Off (0 On)Serchu_29Nessuna valutazione finora

- Titanium Custom 1100a PDocumento13 pagineTitanium Custom 1100a PVictor Rambo100% (1)

- Up/Down counter with latch, overflow latch and adjustable LED brightnessDocumento1 paginaUp/Down counter with latch, overflow latch and adjustable LED brightnessJunaid IqbalNessuna valutazione finora

- SkemaDocumento4 pagineSkemasemang4tNessuna valutazione finora

- An Send EnteDocumento2 pagineAn Send EnteRonald Condori BGNessuna valutazione finora

- Schematic DiagramDocumento13 pagineSchematic DiagramSas WajiNessuna valutazione finora

- Sharp AR FX4 Fax Expansion Kit Parts GuideDocumento10 pagineSharp AR FX4 Fax Expansion Kit Parts GuideJaime RiosNessuna valutazione finora

- Car Monitoring System IPADocumento42 pagineCar Monitoring System IPASaleh AlsaqerNessuna valutazione finora

- Easypic v7 Schematic v104cDocumento2 pagineEasypic v7 Schematic v104cvaldinos100% (1)

- L289N ModuleDocumento1 paginaL289N ModuleHùng NguyenNessuna valutazione finora

- Q9T4 FP91G Interface BDDocumento5 pagineQ9T4 FP91G Interface BDax63naNessuna valutazione finora

- SDR BPFDocumento2 pagineSDR BPFRavindran KodakkattilNessuna valutazione finora

- LCR Metar circuit analysisDocumento7 pagineLCR Metar circuit analysisKarlo MužinićNessuna valutazione finora

- KA2284Documento2 pagineKA2284Adir FigueiredoNessuna valutazione finora

- Bài Tập 1: V C C - 5 VDocumento21 pagineBài Tập 1: V C C - 5 VShin DongNessuna valutazione finora

- Enr L01Documento1 paginaEnr L01William XavierNessuna valutazione finora

- BK BambooDocumento1 paginaBK BambooAT_No1Nessuna valutazione finora

- IO Door Board SchematicDocumento2 pagineIO Door Board Schematicvilla1960Nessuna valutazione finora

- Arduino temperature sensor and LCD display circuitDocumento1 paginaArduino temperature sensor and LCD display circuitVânSơn100% (2)

- AlarmeDocumento1 paginaAlarmeleomar_bNessuna valutazione finora

- Matrix display and control circuit using PIC microcontrollerDocumento1 paginaMatrix display and control circuit using PIC microcontrollerHữu BìnhNessuna valutazione finora

- Mri Airis II MRPSC Cz67ac-S13Documento370 pagineMri Airis II MRPSC Cz67ac-S13Kosmic AdminNessuna valutazione finora

- Electronic Circuit Design Ideas: Edn Series for Design EngineersDa EverandElectronic Circuit Design Ideas: Edn Series for Design EngineersValutazione: 5 su 5 stelle5/5 (2)

- Bellman Ford Dan DisjkartaDocumento5 pagineBellman Ford Dan DisjkartaFarhan S. AdulNessuna valutazione finora

- TUGAS METODE NUMERIK POLINOM LAGRANGEDocumento11 pagineTUGAS METODE NUMERIK POLINOM LAGRANGEFarhan S. AdulNessuna valutazione finora

- Chapter5 NetworkLayerDocumento95 pagineChapter5 NetworkLayerHargyo NugrohoNessuna valutazione finora

- Kode Program No. 1:: Import Java - Math.BigdecimalDocumento5 pagineKode Program No. 1:: Import Java - Math.BigdecimalFarhan S. AdulNessuna valutazione finora

- Bahasa Inggris Three Fish Lived in A PondDocumento1 paginaBahasa Inggris Three Fish Lived in A PondFarhan S. AdulNessuna valutazione finora

- Resep Bahasa InggrisDocumento12 pagineResep Bahasa InggrisFarhan S. AdulNessuna valutazione finora

- SQL Fundamentals for Database Design and Data RetrievalDocumento11 pagineSQL Fundamentals for Database Design and Data RetrievalSan DeepNessuna valutazione finora

- Mainframe230 Blogspot inDocumento4 pagineMainframe230 Blogspot inArunachalam NarayananNessuna valutazione finora

- At Commands For Bluetooth ModuleDocumento19 pagineAt Commands For Bluetooth ModuleKevin Basto100% (1)

- Django - StudentDocumento18 pagineDjango - StudentPraveen GuptaNessuna valutazione finora

- LG Air Conditioners Common Error CodesDocumento2 pagineLG Air Conditioners Common Error CodesnovyNessuna valutazione finora

- Database ConnectionsDocumento17 pagineDatabase ConnectionsDjoelzt TheLucky-boyNessuna valutazione finora

- User's Guide For TV Board V59Documento23 pagineUser's Guide For TV Board V59chackNessuna valutazione finora

- A Thinking Ape Entertainment LTD - Sukhpreet GosalDocumento10 pagineA Thinking Ape Entertainment LTD - Sukhpreet Gosalapi-487587792Nessuna valutazione finora

- Rust Programming Cheat Sheet: IncludesDocumento2 pagineRust Programming Cheat Sheet: IncludesmutecamelNessuna valutazione finora

- A1SD75P1-S3/P2-S3/P3-S3 Positioning Module ManualDocumento616 pagineA1SD75P1-S3/P2-S3/P3-S3 Positioning Module ManualNguyen Thanh DaiNessuna valutazione finora

- FI 1: Display Chart of AccountsDocumento17 pagineFI 1: Display Chart of AccountsMirela MemicNessuna valutazione finora

- asset-v1-Microsoft+AZURE214x+2016 T4+type@asset+block@AZURE214 AzureFundamentals IntroToAzure PracticalExercises PDFDocumento9 pagineasset-v1-Microsoft+AZURE214x+2016 T4+type@asset+block@AZURE214 AzureFundamentals IntroToAzure PracticalExercises PDFMed ManghoumNessuna valutazione finora

- AttachmentDocumento16 pagineAttachmentArest DoiNessuna valutazione finora

- HackyEaster2018 SummaryDocumento96 pagineHackyEaster2018 SummaryCrystal PruebaNessuna valutazione finora

- Image Processing Project SynopsisDocumento16 pagineImage Processing Project SynopsisSumit Chauhan100% (1)

- BN DBNMB DFNB FMDF BDFJHFDJD FBNF DFHB DF GDJ BHB HDFB DFD GHDF BGGH BGH FDocumento14 pagineBN DBNMB DFNB FMDF BDFJHFDJD FBNF DFHB DF GDJ BHB HDFB DFD GHDF BGGH BGH FzuritovNessuna valutazione finora

- Digital Signal Processing Using Matlab 3rd Edition Schilling Solutions ManualDocumento26 pagineDigital Signal Processing Using Matlab 3rd Edition Schilling Solutions ManualJanetMaldonadodnya100% (55)

- Billing Management ConsoleDocumento2 pagineBilling Management ConsoleDita Ravena Putri 01Nessuna valutazione finora

- Software Quality Assurance - For - AppraisalDocumento5 pagineSoftware Quality Assurance - For - AppraisalPravin ThoratNessuna valutazione finora

- Keyboard Shortcuts GuideDocumento15 pagineKeyboard Shortcuts GuidemohanNessuna valutazione finora

- Senior SDET with 6+ Years ExperienceDocumento2 pagineSenior SDET with 6+ Years Experiencehimanshu tiwariNessuna valutazione finora

- 928TCDocumento116 pagine928TCJuan David DiazNessuna valutazione finora

- Domino 7 Performance Tuning Best PracticesDocumento160 pagineDomino 7 Performance Tuning Best PracticesCarlos Choriego GilNessuna valutazione finora

- Developing Enterprise ArchitectsDocumento12 pagineDeveloping Enterprise ArchitectskikinjoNessuna valutazione finora

- OMNet 4.0 ManualDocumento361 pagineOMNet 4.0 ManualHari KrishnaNessuna valutazione finora

- Smoke Test Mind Map PDFDocumento1 paginaSmoke Test Mind Map PDFmeet kajanaNessuna valutazione finora

- Xilinx XC9572Documento9 pagineXilinx XC9572Yacine AlgersNessuna valutazione finora

- ATC Involuntary Reissue GuideDocumento2 pagineATC Involuntary Reissue GuideDaniela Iuliana Mihaltu100% (1)

- Setting up SSH and SCP securelyDocumento2 pagineSetting up SSH and SCP securelya17fanNessuna valutazione finora