Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

KSZ8021RNL - KSZ8031RNL Eval Board Schematic Rev1.1

Caricato da

Anonymous 60esBJZIjTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

KSZ8021RNL - KSZ8031RNL Eval Board Schematic Rev1.1

Caricato da

Anonymous 60esBJZIjCopyright:

Formati disponibili

1

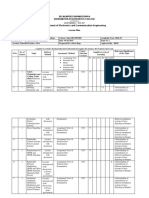

KSZ8021RNL / KSZ8031RNL Eval Board Revision 1.0

REVISION HISTORY DATE

5/8/10 7/28/10

Table of Contents

REVISION

1.0 1.1

DESCRIPTION

Initial Customer Release Changed R5 (INTRP pull-up) from NC to 4.7K. Deleted R43 and R44 (both re-work resistors are no longer needed).

PAGE PAGE PAGE PAGE

01: 02: 03: 04:

Revision History KSZ8021/31RNL Eval Board -- Block Diagram KSZ8021/31RNL Device / UTP Interface / RMII Port USB Port for MDC/MDIO Register Access

CONFIDENTIAL & PROPRIETARY

Title

KSZ8021RNL / KSZ8031RNL Eval Board Revision 1.0

Size Date:

1 2 3 4

Document Number

Revision History

Wednesday, July 28, 2010 Sheet

5

Rev 1.1 1 of 4

KSZ8021RNL / KSZ8031RNL EVAL BOARD - BLOCK DIAGRAM

D D

3.3V LDO

1.8V/2.5V VDDIO LDO (option)

5V LDO (option for USB)

USB Port * 5V DC Power Input * MDC/MDIO PHY Register Access

USB_5.0V (input power from USB Port) Voltage Translator

RMII_5.0V (input power from RMII Port)

RESET

C C

Jumpers

Port Status LED Indicator

MDC / MDIO

Pulse H1102

25/50 MHz System Clock option

24-pin QFN

B

Jumpers to select RMII Loopback Test Option

10Base-T / 100Base-TX RJ-45 Jack

Magnetics

TX / RX pairs

KSZ8021RNL / KSZ8031RNL

RMII Signals

RMII Port Connector

25 MHz XTAL

25/50 MHz Oscillator option

Device - RMII Configuration

Power-up default (unmanaged setting) KSZ8021RNL

A

Populate R17, R19 R11, C16, C17, Y1

Do Not Populate R11, C16, C17, Y1

A

50MHz clock input to XI (pin 8) 25MHz crystal / clock input to XI (pin 8) 50MHz RMII reference clock output from REF_CLK (pin 16)

KSZ8031RNL

R17, R19

CONFIDENTIAL & PROPRIETARY

Title

NOTE: After power-up, both devices can be programmed via MDC/MDIO bus to either 25MHz or 50MHz clock input mode.

KSZ8021RNL / KSZ8031RNL Eval Board Revision 1.0

Size Date:

1 2 3 4

Document Number

KSZ8021/31RNL Eval Board - Block Diagram

Wednesday, July 28, 2010 Sheet

5

Rev 1.1 4

of

1.8V / 2.5V option for KSZ8021/31RNL VDDIO power.

RMII Loopback Test Option

3.3V U2

MIC5207YM5

1 C1 + 10uF

D

SYS_CLK_BTB TP1

1.8V_2.5V RMII_5.0V

5 R1 + BYP/ADJ 4 C5 1 3 470pF 1.50K 10uF 0.1uF C4 C3

5.0V U3 JP1

1 2 3 1 C6 + 47uF/16V TANT C C9 0.1uF

3.3V

1. Close jumpers (J1, J2, J3). 2. Program KSZ8021/31RNL for RMII Back-to-Back mode by setting register 22 (16h) bit [6] to '1'.

TP2

GND

VIN GND EN

VOUT

2 C2 3 0.1uF

USB_5.0V

MIC39100-3.3WS / SOT-223

IN OUT 3 C7 + 47uF / TANT C C8 0.1uF

CRS_DV_RMII RXD0_RMII RXD1_RMII

J1 J2 J3

JUMPER JUMPER JUMPER

TXEN_RMII TXD0_RMII TXD1_RMII

D

GND

3X1

R2 R3 1.50K

TAB

JP2

3X1

GND

Align test points horizontally in between jumpers

MDC MDIO

TP3 TP4

5V DC Input Power Select

RMII_5.0V : close pins 1, 2 USB_5.0V : close pins 2, 3 1.8V : close pins 1, 2 2.5V : close pins 2, 3

For Adjustable Voltage Regulator (MIC5207YM5), use following formula to set VOUT.

680

VOUT = 1.24 X [ 1 + ( Rsel / R1 ) ]

Rsel = R2 or R3

RMII Mode

VDDA_3.3 VDDIO

The RMII signal connections between KSZ8021/31RNL PHY and external MAC are shown in the table to the right. For RMII mode with 25MHz XTAL input and 50MHz RMII Reference Clock output, 1.8V_2.5V : close pins 1, 2 3.3V : close pins 2, 3 1. Connect J4 (RMII Port) to board with RMII MAC (e.g. Micrel KSZ8893MQL Eval Board). 2. Program KSZ8021/31RNL for RMII mode with 25MHz XTAL input and 50MHz RMII Reference Clock output. 3. Program other KSZ8021/31RNL configuration settings (ISOLATE, B-CAST_OFF, NWAYEN, SPEED, DUPLEX) to desired settings.

KSZ8021/31RNL PHY RMII Signals

Name REF_CLK Pin # 16 19 21 20 15 12 13 17 Type Output Input Input Input Output Output Output Output

KSZ88x3 MAC RMII Signals

Name REF_CLK CRS_DV RXD1 RXD0 TX_EN TXD1 TXD0 TXER Type Input Output Output Output Input Input

C

3.3V

Notes:

1. KSZ8021/31RNL has a Paddle Ground on bottom side of chip. Refer to datasheet for mechanical dimensions. 2. KSZ8021/31RNL provides the 1.2V supply for VDD_1.2 (pin 1). Decouple 1.2V power rail as shown. 3. Place components (Y1, C16, C17, C18, R15) close to respective pins of U1.

C10 C11 RST# LED0 2.2uF

STEWARD HI1206N101R-00

FB1 1 FBEAD 2

3.3V

1.8V_2.5V

JP3

1 2 3

R4 220 2

TX_EN TXD1 TXD0 CRS_DV RXD1 RXD0 RXER

D1

POWER_ON LED

3X1

VDD_1.2

TXD1 TXD0 TXEN + 0.1uF

Board

Input Input

VDDIO

VDDIO

TP5

LED Mode

LED0

[00]

LINK/ACT

[01]

LINK

C14

VDDA_3.3

25 24 23 22 21 20 19 + C12 22uF C13 0.1uF INTRP R5 4.7K

C15 22uF

3.3V

LED1 1 LEDx1 2 R8 220 LED0

0.1uF

P_GND

RST# LED0 GND TXD1 TXD0 TXEN

RMII_5.0V

TXD1 RXM RXP TXM TXP 1 2 3 4 5 6 VDD_1.2 VDDA_3.3 RXM RXP TXM TXP INTRP RXER REF_CLK CRS_DV VDDIO RXD0 18 17 16 15 14 13 INTRP RXER REF_CLK CRS_DV RXD0 TXD0 TXEN

R6 R7 R9

0 0 0

TXD1_RMII TXD0_RMII TXEN_RMII 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

J4

VCC CRS COL TXD3 TXD2 TXD1 TXD0 TX_EN TX_CLK TX_ER RX_ER RX_CLK RX_DV RXD0 RXD1 RXD2 RXD3 MDC MDIO VCC VCC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC VCC 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

RXER XO XI REXT MDIO MDC RXD1

R10 R11 R12 R13 R14

49.9 49.9 49.9 49.9 49.9

RXER_RMII REF_CLK_RMII CRS_DV_RMII RXD0_RMII RXD1_RMII

System Clock options Layout SMD footprint ECS-3953M-250-BN (25MHz 50ppm) ECS-3953M-500-BN (50MHz 50ppm)

B

Device - RMII Configuration

See Table on schematic page 2.

TXD1_RMII TXD0_RMII TXEN_RMII RXER_RMII REF_CLK_RMII CRS_DV_RMII RXD0_RMII RXD1_RMII MDC MDIO

REF_CLK

U1 KSZ8021RNL / KSZ8031RNL

RXD1 MDC MDIO MDC MDIO (4) (4)

CRS_DV RXD0 RXD1

XO XI C16 22pF C17 REXT C18 NC R15 6.49K

7 8 9 10 11 12

Y1 25MHz

Place 0402 resistors on Component Side

22pF

VDDIO

4 1 + C19 10uF C20 10nF

VDDIO

Male RMII Connector RMII Port

R19 NC / 0 R21

Y2

VCC NC OUT GND 3

R18 R16 R17 1.0K NC / 49.9 NC / 0 SYS_CLK R20 NC / 49.9

25/50MHz +/-50ppm

25/50MHz System Clock net to/from connecting board

NC / 0 SYS_CLK SYS_CLK_BTB

ENET_CGND

Place GND test points evenly across PCB. T1 Pulse H1102

TP9

1 2 3 6 7 8 RXM RST# C22 0.1uF C23 0.1uF C24 + SW PUSHBUTTON 10uF / TANT A Title 1 3 TXM RXP R26 10K 2 1 D2

A

TH1 TH2

TP8 GND GND

TP10 GND

TP11 GND

J5

A

8 7 6 5 4 3 2 1

R22 RXR24 RX+ TXTX+

75 75 C21

R23 R25

75 75

CMT CMR

TX+ CMT TXRX+

16 15 14 11 10 9

TXP

VDDIO

PHY Hardware Reset Active Low

1000pF / 2kV

RJ-45 Jack

1

FB2 2 FBEAD ENET_CGND

STEWARD HI1206N101R-00

GND

CMR RX-

BAV16W-7 SOD-123

S1 2 4

CONFIDENTIAL & PROPRIETARY

KSZ8021RNL / KSZ8031RNL Eval Board Revision 1.0

Size Date: Document Number

Place ferrite bead ground bridge for ENET_CGND to GND (signal ground) return close to GND at input power to board.

KSZ8021/31RNL Device / UTP Interface / RMII Port

Wednesday, July 28, 2010

5

Rev 1.1 4

Sheet

of

5.0V

U4

MIC5207-5.0YM5

1 VIN GND EN BYP/ADJ 4

C34 470pF

STEWARD HI1206N101R-00

FB3

5V_Reg

5V_USB U5 - FTDI FT2232D Decouple Pins (3, 42)

C28 + 10uF / TANT A C29 0.1uF C30 0.1uF

3.3V

STEWARD HI1206N101R-00

FB4

3.3V_USB U5 - FTDI FT2232D Decouple Pins (14, 31)

C31 + 10uF / TANT A 0.1uF 0.1uF

D

VOUT

5

C26 + 10uF / TANT A 0.1uF C27

1

FBEAD

1

FBEAD

2

C32 C33

C25

D

2 3

1.0uF

C35

27pF XTIN

MIC5207-5.0YM5 has very low dropout voltage (typically 165mV @ 150mA). FTDI FT2232D can operate down to +4.35V for its 5V input power (5V_USB).

C36 27pF

Y3 6MHz

XTOUT

MDC / MDIO Voltage Translator 5V_Reg 5V_USB

C37

3.3V_USB

VDDIO 3.3V_USB

R27 R28 4.7K R29 4.7K

C

5V_USB

C

USB_5.0V

JP4

1 2 3

R33

0.1uF R30 R31 470 1K 4.7K MDC_PHY 4.7K R32

U5

TI PCA9306

1 2 3 4 GND VREF1 SCL1 SDA1 EN VREF2 SCL2 SDA2 8 7 6 5

200K

3X1

MDC_USB MDIO_USB C38 0.1uF

USB_5.0V (USB Port Powered) * close JP4 pins 2, 3 * close JP5 pins 1, 2

R34

JP5

1 2 3

48 47 46 45 44 43 42 41 40 39 38 37

3.3V_USB

U6 FTDI FT2232D

EECS TEST AVCC AGND XTOUT XTIN VCC PWREN# NC NC NC NC

MDIO_PHY

VSSOP-DCU

R35 10K

RMII_5.0V (RMII Port Powered) * close JP4 pins 1, 2 * close JP5 pins 2, 3

3X1

4.7K RESET#_USB RSTOUT# 3V3OUT USBDP USBDM

R36 10K

B

C39 33nF

USB_5.0V

2

1 2 3 4 5 6 7 8 9 10 11 12

EESK EEDATA VCC RESET# RSTOUT# 3V3OUT USBDP USBDM GND NOT_USED GPIOH3 GPIOH2

NC NC GND NC NC VCCIOB NC NC NC NC NOT_USED GND

36 35 34 33 32 31 30 29 28 27 26 25

3.3V_USB

R37 10K

B

FB5 FBEAD

STEWARD HI1206N101R-00

R38

GPIOH1 VCCIOA GPIOH0 GPIOL3 GPIOL2 GND GPIOL1 GPIOL0 TMS/CS TDO/D1 TDI/D0 TCK/SK

USB Port - MDC / MDIO Access * close JP6, JP7 RMII Port - MDC / MDIO Access * open JP6, JP7

3.3V_USB

10K

C40

CN1

CN-USB

1 2 3 4

R40 R41

10nF JP6 R39 27 0805 27 0805 1.5K RSTOUT# USBDM USBDP R42 0 MDC_USB MDIO_USB MDC_PHY MDIO_PHY

13 14 15 16 17 18 19 20 21 22 23 24

1 1

JP7

2 2

MDC MDIO

MDC MDIO

(3) (3)

5

A

STEWARD HI1206N101R-00

FB6

CONFIDENTIAL & PROPRIETARY

USB Configuration * Multi-Protocol Synchronous Serial Engine (MPSSE) Mode

Size Date: Title

1

FBEAD USB_CGND

KSZ8021RNL / KSZ8031RNL Eval Board Revision 1.0

Document Number

USB Port for MDC/MDIO Register Access

Wednesday, July 28, 2010 Sheet

5

Rev 1.1 of 4

Potrebbero piacerti anche

- Q 200101Documento180 pagineQ 200101Anonymous 60esBJZIjNessuna valutazione finora

- Q 200107Documento180 pagineQ 200107Anonymous 60esBJZIjNessuna valutazione finora

- Amateur RadioDocumento180 pagineAmateur RadioAnonymous 60esBJZIjNessuna valutazione finora

- HRH - 00 Supplement 1977Documento32 pagineHRH - 00 Supplement 1977Anonymous 60esBJZIjNessuna valutazione finora

- Q 200103Documento180 pagineQ 200103Anonymous 60esBJZIjNessuna valutazione finora

- Q 200003Documento180 pagineQ 200003Anonymous 60esBJZIjNessuna valutazione finora

- Q 200106Documento180 pagineQ 200106Anonymous 60esBJZIjNessuna valutazione finora

- Arrl - QST Magazine - QRP in ApartmentsDocumento4 pagineArrl - QST Magazine - QRP in ApartmentsAnonymous 60esBJZIjNessuna valutazione finora

- Nationa Contest JournalDocumento68 pagineNationa Contest JournalAnonymous 60esBJZIjNessuna valutazione finora

- Stolces J. 70 Years of Radio Tubes and Valves 2ed 1997 - Part4Documento20 pagineStolces J. 70 Years of Radio Tubes and Valves 2ed 1997 - Part4Anonymous 60esBJZIjNessuna valutazione finora

- Stolces J. 70 Years of Radio Tubes and Valves 2ed 1997 - Part5Documento20 pagineStolces J. 70 Years of Radio Tubes and Valves 2ed 1997 - Part5Anonymous 60esBJZIjNessuna valutazione finora

- Stolces J. 70 Years of Radio Tubes and Valves 2ed 1997 - Part1Documento20 pagineStolces J. 70 Years of Radio Tubes and Valves 2ed 1997 - Part1Anonymous 60esBJZIjNessuna valutazione finora

- Arrl - QST Magazine - Low Power, Crummy AntennaDocumento6 pagineArrl - QST Magazine - Low Power, Crummy AntennaAnonymous 60esBJZIjNessuna valutazione finora

- Arrl - QST Magazine - Principles of Radiotelephony - Part 2 (1954)Documento4 pagineArrl - QST Magazine - Principles of Radiotelephony - Part 2 (1954)Anonymous 60esBJZIjNessuna valutazione finora

- Arrl - QST Magazine - Principles of Radiotelephony - Part 3 (1954)Documento7 pagineArrl - QST Magazine - Principles of Radiotelephony - Part 3 (1954)Anonymous 60esBJZIjNessuna valutazione finora

- G.654 Characteristics of A Cut-Off Shifted Single-Mode Optical Fibre and CableDocumento22 pagineG.654 Characteristics of A Cut-Off Shifted Single-Mode Optical Fibre and CableAnonymous 60esBJZIjNessuna valutazione finora

- G.653 Characteristics of A Dispersion-Shifted Single-Mode Optical Fibre and CableDocumento22 pagineG.653 Characteristics of A Dispersion-Shifted Single-Mode Optical Fibre and CableAnonymous 60esBJZIjNessuna valutazione finora

- G.650.2 Definitions and Test Methods For Statistical and Non-Linear Related Attributes of Single-Mode Fibre and CableDocumento80 pagineG.650.2 Definitions and Test Methods For Statistical and Non-Linear Related Attributes of Single-Mode Fibre and CableAnonymous 60esBJZIjNessuna valutazione finora

- Test Equipment Solutions DatasheetDocumento7 pagineTest Equipment Solutions DatasheetAnonymous 60esBJZIjNessuna valutazione finora

- Alpha ManualDocumento8 pagineAlpha ManualAnonymous 60esBJZIjNessuna valutazione finora

- C and L Band EDFA Control Software User's ManualDocumento12 pagineC and L Band EDFA Control Software User's ManualAnonymous 60esBJZIjNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- M.tech ADC New Lesson Plan - 2018-19Documento12 pagineM.tech ADC New Lesson Plan - 2018-19Rvh PrasadNessuna valutazione finora

- Pexip Infinity Installation ChecklistDocumento2 paginePexip Infinity Installation ChecklistBogdanDragomirNessuna valutazione finora

- RPG IV Socket TutorialDocumento171 pagineRPG IV Socket TutorialanupgiriNessuna valutazione finora

- Sap Abap QUESTION /ANSWERDocumento3 pagineSap Abap QUESTION /ANSWERVikrant KaushalNessuna valutazione finora

- Architecture: SAP R/3 Workload AnalysisDocumento5 pagineArchitecture: SAP R/3 Workload AnalysispapusahaNessuna valutazione finora

- GridDocumento42 pagineGridgopitheprinceNessuna valutazione finora

- J1939 Training: - AgendaDocumento72 pagineJ1939 Training: - AgendaRafael Cardenas100% (4)

- PaperDocumento17 paginePaperNgoc Nguyen100% (1)

- The Most Popular BrowsersDocumento16 pagineThe Most Popular BrowsersAjay JhaNessuna valutazione finora

- Ume pl70 Eng 1362430290Documento323 pagineUme pl70 Eng 1362430290Wilber LucasNessuna valutazione finora

- Google Search HackDocumento4 pagineGoogle Search Hackbalakarthickpbsm100% (3)

- Chat Log SampDocumento14 pagineChat Log SampAnonymous SaLWoIgABHNessuna valutazione finora

- Aradial ManualDocumento101 pagineAradial ManualVivek YadavNessuna valutazione finora

- Internet of Things (IoT)Documento6 pagineInternet of Things (IoT)Kunal KishoreNessuna valutazione finora

- IPVS DesignGuideDocumento243 pagineIPVS DesignGuideLawrence MagureNessuna valutazione finora

- Archer TX50E (UN) - 1.0 DatasheetDocumento5 pagineArcher TX50E (UN) - 1.0 DatasheetMuhammad IrfanNessuna valutazione finora

- GSM Based Automation of Street LightDocumento9 pagineGSM Based Automation of Street LightsrisrinuNessuna valutazione finora

- SRW2224G4 K9Documento1 paginaSRW2224G4 K9koushik42000Nessuna valutazione finora

- Os9 Bab60 1a SoftwDocumento80 pagineOs9 Bab60 1a Softwgarysun585Nessuna valutazione finora

- Review of Error Detection of Data Link Layer in Computer NetworkDocumento7 pagineReview of Error Detection of Data Link Layer in Computer NetworkShweta ONessuna valutazione finora

- OMS V9.5.16 Release NoteDocumento27 pagineOMS V9.5.16 Release Noteroberd_leeNessuna valutazione finora

- InstallDocumento3 pagineInstallEko Setiawan Qurani0% (1)

- Chapter 1 Critical Thinking AnswersDocumento12 pagineChapter 1 Critical Thinking Answersapi-347135684Nessuna valutazione finora

- Usb CongDocumento3 pagineUsb CongVirgie IegrivNessuna valutazione finora

- ZX-Bluetooth Module PDFDocumento10 pagineZX-Bluetooth Module PDFashwanisingla013Nessuna valutazione finora

- Interference AnalysisDocumento5 pagineInterference AnalysisABHILASHNessuna valutazione finora

- CP 3Documento4 pagineCP 3PraneethNessuna valutazione finora

- CEH Lab GuideDocumento116 pagineCEH Lab GuideArpan DasguptaNessuna valutazione finora

- Getting Started With Hapi - Js - Sample ChapterDocumento23 pagineGetting Started With Hapi - Js - Sample ChapterPackt PublishingNessuna valutazione finora

- Dimensions in Data Processing 2402Documento76 pagineDimensions in Data Processing 2402Vishwa PathakNessuna valutazione finora