Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Texas Instruments Incorporated: TMS320VC5402 DSK

Caricato da

0106062007Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Texas Instruments Incorporated: TMS320VC5402 DSK

Caricato da

0106062007Copyright:

Formati disponibili

5

REVISIONS

REV

DESCRIPTION

DATE

APPROVED

LAST USED REFERENCES

R178

CT20

C122

U42

JP4

J9

D8

L8

SW2

RN3

TP13

MT5

F1

P2

Y2

PG TITLE

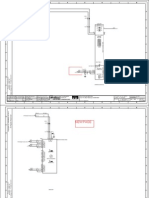

1. COVER SHEET (THIS PAGE)

2. CONNECTORS

3. PARALLEL PORT

4. JTAG

5. VOLTAGE TRANSLATION

6. CPLD

7. CLOCKS

8. DSP

9. BUFFERS

10. MEMORY DECODE

11. MEMORY

12. UART & RS232

13. DAA

14. SPEAKER & MICROPHONE

15. AUDIO CODECS

16. BSP MUX

17. EXPANSION BUFFERS

18. EXPANSION DB INTERFACE

19. RESET CIRCUITRY

20. LEDS/DIP SWITCHES

21. INPUT POWER & GROUND

22. DSP DECOUPLING CAPS

UNUSED REFERENCES

R87

R97

DWN

REVISION STATUS OF SHEETS

G.S. Vestal

DATE

09/22/99

DATE

G.S. Vestal

DATE

09/22/99

DATE

REV

CHK

SH

21

22

ENGR

ENGR-MGR

REV

SH

11

12

13

14

15

16

17

18

19

20

REV

SH

10

NEXT ASSY

QA

DATE

MFG

DATE

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

USED ON

RLSE

Size

B

DATE

APPLICATION

Date:

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

of

22

PARALLEL PORT

SERIAL PORT

TELEPHONE LINE (RJ-11)

P2

13

25

12

24

11

23

10

22

9

21

8

20

7

19

6

18

5

17

4

16

3

15

2

14

1

PP_S6

PP_D7

PP_D6

PP_D5

PP_D4

PP_D3

PP_C3#

PP_D2

PP_C2

PP_D1

PP_S3

PP_D0

PP_C1#

PP_C0#

P1

1

6

2

7

3

8

4

9

5

S_DCD

S_DSR

S_RXD

S_RTS

S_TXD

S_CTS

S_DTR

S_RI

RING

L6

HZ0805E601R

1

PP_S7#

L5

HZ0805E601R

J7

C84

220pF

2KV

1

2

3

4

5

6

PP_S5

AGND

TIP

CONNECTOR DB9M

L8

HZ0805E601R

RING

TIP

RJ-11

PP_S4

C85

220pF

L7

2KV

HZ0805E601R

AGND

DGND

C

PARALLEL PORT

(DB25M)

DGND

MIC IN

SPEAKER OUT

J6

J4

MIC_IN

ST-3120-5B

SPEAKER_OUT

ST-3120-5B

3.5 MM

AUDIO

JACK

3.5 MM

AUDIO

JACK

AGND

AGND

CONNECTORS

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

of

22

PARALLEL PORT INTERFACE

44

43

42

PP_CS3#

PP_CS2#

HPI_CS#

TBC_CS#

87

86

85

84

PP_A[0..4]

PP_A4

PP_A3

PP_A2

PP_A1

PP_A0

PP_SRD#

PP_SWR#

BH_AD15

BH_AD14

BH_AD13

BH_AD12

BH_AD11

BH_AD10

BH_AD9

BH_AD8

BH_AD7

BH_AD6

BH_AD5

BH_AD4

BH_AD3

BH_AD2

BH_AD1

BH_AD0

73

74

75

76

77

78

79

80

88

89

51

52

53

54

55

56

57

58

61

62

63

64

65

66

67

68

50

98

BH_AD[0..15]

32

31

97

46

99

100

95

35

ST0

ST1

ST2

YIN

YOUT

XOUT

TC

69

70

47

48

49

DREQ

IRQ

SLCTD

RESERVED

TEST

SRST

LBAT

H_TCK

H_TMS

H_TDI

MA9

MA8

93

92

PIEZO

DACK

CAS

RAS

38

45

H_IRQ_PP

5V

XIN

SENSE

RESET

SRST

IN0

IN1

IN2

IN3

CS3

CS2

CS1

CS0

IO16

WDOGEN

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

HSLCT

HPE

HBSY

HACK

HD7

HD6

HD5

HD4

SRD

SWR

HD3

HSEL

HD2

HINIT

HD1

HERR

HD0

SD15

SD14

SD13

SD12

SD11

SD10

SD9

SD8

SD7

SD6

SD5

SD4

SD3

SD2

SD1

SD0

HALF

HSTB

PSLCT

PPE

PBSY

PACK

PERR

PSTB

PALF

PINIT

PSEL

PID

BCLK

96

33

34

94

82

83

37

36

PP_SCLK

R91

10K

5V

BRD_RST#

H_SRST

TBC_RDY#

TBC_INT#

R160

8-Bit Transfer

10K

H_TDO

81

39

30

28

26

24

20

18

17

16

PP_S4

PP_S5

PP_S7#

PP_S6

PP_D7

PP_D6

PP_D5

PP_D4

15

14

13

11

8

6

5

PP_D3

PP_C3#

PP_D2

PP_C2

PP_D1

PP_S3

PP_D0

3

2

PP_C1#

PP_C0#

1

4

7

12

25

29

27

23

19

Pass Thru Interface

PARALLEL PORT INTERFACE POWER

5V

U32B

B

BH_AD1

R132 10K

U32A

BH_AD10

R115 10K

PPC34C60

BH_AD12

R107 10K

BH_AD14

R101 10K

VCC

VCC

VCC

VCC

VCC

VCC

9

21

41

60

72

90

PID for 5402

RN1

R8

R7

R6

R5

R4

R3

R2

R1

5V

10

5

COM2

COM1

9

8

7

6

4

3

2

1

BH_AD15

BH_AD14

BH_AD13

BH_AD12

BH_AD11

BH_AD10

BH_AD9

BH_AD8

PP_BCLK

GND

GND

GND

GND

GND

GND

C80

C67

C81

C95

C109

C94

0.01uF

0.01uF

0.01uF

0.01uF

0.01uF

0.01uF

91

71

59

40

22

10

745101103JTR

PPC34C60

DGND

RN2

A

10

5

R8

R7

R6

R5

R4

R3

R2

R1

COM2

COM1

9

8

7

6

4

3

2

1

BH_AD7

BH_AD6

BH_AD5

BH_AD4

BH_AD3

BH_AD2

BH_AD1

BH_AD0

TEXAS INSTRUMENTS INCORPORATED

Title

PARALLEL PORT INTERFACE

TMS320VC5402 DSK

Size

B

745101103JTR

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

of

22

JTAG PASS THRU

TBC_TDO

R59 0

TBC_TDI

R64 0

TBC_TCK

R57 0

TBC_TMS

R62 0

TBC_EMU0

R13 0

TBC_EMU1

R11 0

TBC_TRST#

R19 0

DSP_TDI

DSP_TDO

D

DSP_TCK

DSP JTAG HEADER

3.3V

DSP_TMS

J2

XDS_TMS

XDS_TDI

DSP_EMU0

DSP_EMU1

XDS_TDO

XDS_TCK

DSP_TRST#

NOTE: Resistors only installed if mux's not installed.

XDS_EMU0

5V

5V

1

3

5

7

9

11

13

2

4

6

8

10

12

14

XDS_TRST#

4.3V

XDS_EMU1

TSW-107-14-G-D-006

C50

5V

0.1uF

DGND

C26

C11

C40

0.1uF

0.1uF

0.1uF

DGND

DGND

U11

VCC

TBC_TDI

XDS_TDO

TBC_TDO

XDS_TDI

TBC_TCK

XDS_TCK

TBC_TMS

XDS_TMS

DGND

1

15

BH_AD[0..15]

BH_AD0

BH_AD1

BH_AD2

BH_AD3

BH_AD4

BH_AD5

BH_AD6

BH_AD7

BH_AD8

BH_AD9

BH_AD10

BH_AD11

BH_AD12

BH_AD13

BH_AD14

BH_AD15

2

3

4

5

6

7

8

9

10

11

14

15

16

17

18

19

20

21

22

24

25

TBC_WR#

TBC_RD#

41

42

TBC_CLK

29

VCC2

VCC1

VCC0

PP_A[0..4]

PP_A0

PP_A1

PP_A2

PP_A3

PP_A4

ADRS0

ADRS1

ADRS2

ADRS3

ADRS4

2

3

5

6

11

10

14

13

R28

10K

35

23

13

JTAG CONTROLLER

(TBC)

U17

TOFF#

R66

360

26

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

1A

2A

3A

4A

DGND

16

4

DSP_TDO

DSP_TDI

DSP_TCK

12

DSP_TMS

S

OE

GND

SN74CBT3257

TDI0

TDI1

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

TDO

TCK0

4.3V

27

DGND

28

C25

31

JTAG MULTIPLEXERS

30

0.1uF

U9

TMS0

TMS1

TMS2/EVENT0

TMS3/EVENT1

TMS4/EVENT2

TMS5/EVENT3

VCC

33

2

3

5

6

11

10

14

13

TBC_EMU0

XDS_EMU0

TBC_EMU1

XDS_EMU1

TBC_TRST#

XDS_TRST#

36

37

38

39

1

15

S_JTAGSEL

WR#

RD#

TCKI

INT#

32

44

R30

360

TBC_INT#

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

1A

2A

3A

4A

DGND

16

4

7

DSP_EMU0

DSP_EMU1

12

DSP_TRST#

S

OE

GND

40

TRST#

1

12

34

TBC_RST#

GND0

GND1

GND2

SN74CBT3257

RDY#

43

TBC_RDY#

DGND

SN74ACT8990

DGND

TEXAS INSTRUMENTS INCORPORATED

JTAG

Title

TMS320VC5402 DSK

Size

B

Date:

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

of

22

CPLD ISR HEADER

5V

NOTE: DO NOT INSTALL THESE COMPONENTS.

HPI-DATA VOLTAGE TRANSLATION

J1

1

3

5

7

9

ISR_TDO

1

3

5

7

9

2

4

6

8

10

2

4

6

8

10

5V

ISR_TMS

ISR_TCK

ISR_TDI

C79

U24

TSW-105-07-G-D

DGND

Vcc

DGND

H_AD[0..7]

H_AD0

H_AD1

H_AD2

H_AD3

H_AD4

3

4

7

8

11

H_AD5

H_AD6

H_AD7

14

17

18

21

22

CPLD ISR SOURCE SELECTION

4.3V

NOTE: DO NOT INSTALL THESE COMPONENTS.

13

C44

R114

360

0.1uF

12

5V

R6

JP1

HDR

PCI

10K

1

2

3

DGND

TSW-103-07-G-S

VCC

2

3

5

6

11

10

14

13

H_TCK

ISR_TCK

H_TMS

ISR_TMS

H_TDO

ISR_TDO

H_TDI

ISR_TDI

1

15

8

R61

360

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

1A

2A

3A

4A

1A1

1A2

1A3

1A4

1A5

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

2A1

2A2

2A3

2A4

2A5

CPLD_TCK

CPLD_TMS

CPLD_TDO

12

GND

CPLD_TDI

HPI-CTRL VOLTAGE TRANSLATION

5V

C39

GND

U12

H_TCK

0.1uF

H_CS0#

H_DS2#

H_DS#

H_R/W#

H_HWIL

3

4

7

8

11

H_CNTL0

H_CNTL1

14

17

18

21

22

CPLD_TCK

H_TMS

13

CPLD_TMS

R49

R56

S

OE

ISR SOURCE MUX BYPASS

BH_AD5

BH_AD6

BH_AD7

DGND

15

16

19

20

23

BH_AD[0..15]

16

DGND

R53

BH_AD0

BH_AD1

BH_AD2

BH_AD3

BH_AD4

2OE

SN74CBT3257

R60

2

5

6

9

10

1OE

Vcc

DGND

24

SN74CBTD3384

U13

DGND

0.1uF

H_TDO

R14

CPLD_TDO

H_TDI

12

360

1A1

1A2

1A3

1A4

1A5

1B1

1B2

1B3

1B4

1B5

24

DGND

2

5

6

9

10

HPI_CS#

PP_SWR#

PP_SRD#

PP_A0

PP_A1

15

16

19

20

23

PP_A2

PP_A3

1OE

2A1

2A2

2A3

2A4

2A5

2B1

2B2

2B3

2B4

2B5

2OE

GND

SN74CBTD3384

CPLD_TDI

NOTE: Resistors only installed if above mux not installed.

DGND

TEXAS INSTRUMENTS INCORPORATED

5V / 3.3V TRANSLATION & CPLD HEADER

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

of

22

CPLD_TCK

CPLD_TMS

CPLD_TDO

CPLD_TDI

MEMORY DECODING & GLUE LOGIC

BH_AD[0..15]

D

PP_A[0..4]

MP_MC

DS

PS

IS

IOSTRB

MSTRB

R/W

DB_IO0

DB_IO1

DB_IO2

DB_IO3

DB_DET

M

E

M

DB_IS

DB_PS

DB_DS

DM_PG4

DM_PG3

DM_PG2

DM_PG1

DM_PG0

DM_SEL

X

C

V

R

DATA2XD

DB_ABCE

DB_ABLE

DB_ABOE

DB_BACE

DB_BALE

DB_BAOE

X_CNTL0

X_CNTL1

X_STAT0

X_STAT1

DB_DET#

104

105

119

132

150

70

69

7

35

R47

R22

R58

103

110

109

114

112

108

106

R54

R27

R21

R33

R16

R26

R29

45.3, 1%

45.3, 1%

45.3, 1%

45.3, 1%

45.3, 1%

45.3, 1%

45.3, 1%

45.3, 1%

45.3, 1%

45.3, 1%

20

40

60

62

80

100

120

140

142

160

6

46

76

116

139

JTAG

TBC_RD#

TBC_WR#

TBC_CS#

PP_SRD#

PP_SWR#

PP_CS2#

PP_CS3#

PP_BCLK

28

26

126

16

22

92

83

99

FC1

FC2

68

153

SRAM_CE#

X_IS#

X_PS#

X_DS#

DM_PG4

DM_PG3

DM_PG2

DM_PG1

DM_PG0

DM_SEL#

FLASH_CE#

DATA2XD#

DB_ABCE#

DB_ABLE#

DB_ABOE#

DB_BACE#

DB_BALE#

DB_BAOE#

45.3, 1%

R96

36

45.3, 1%

R95

27

UART_CE#

UART_RD#

UART_WR#

115

30

33

DAA_OH#

DAA_RING#

DAA_CID#

82

97

11

TBC_RD

TBC_WR

TBC_CS

PP_RD

PP_WR

PP_CS2

PP_CS3

PP_BCLK

P

P

C

A

D

FC1

FC2

SRAM_CE

FLASH_CE

UART_CE

UART_RD

UART_WR

DAA_OH

DAA_RING

DAA_CID

POWER

C

N

T

L

CY3712 8VP

CPL D

TEST

FLOAT#

38

S

P

A

R

E

S

PIN3

PIN8

PIN12

PIN24

PIN25

PIN37

PIN53

PIN54

PIN55

PIN77

PIN78

PIN79

PIN89

PIN91

PIN117

PIN118

PIN137

PIN138

PIN152

3

8

12

24

25

37

53

54

55

77

78

79

89

91

117

118

137

138

152

D

A

A

GROUNDS

FLOAT

CY37128

CY37128

CPLD PULL-UP RESISTORS

3.3V

3.3V

R70

10K

R74

10K

R48

10K

BDSP_ADDR[0..22]

BDSP_DATA[0..15]

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

14

75

66

149

95

TCK

TMS

TDO

TDI

DSP_NMI#

DSP_INT0#

DSP_INT1#

DSP_INT2#

DSP_INT3#

X_INT0#

X_INT1#

X_INT2#

X_INT3#

X_DBINT#

UART_INT

BOOT_INT#

H_IRQ_PP

H_INT0#

JTAGEN

BH_AD0

BH_AD1

BH_AD2

BH_AD3

BH_AD4

BH_AD5

BH_AD6

BH_AD7

42

32

23

58

43

128

129

57

DSP

D

B

135

154

125

39

143

133

124

156

17

64

48

88

29

134

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

59

86

49

148

19

155

4

DSP_NMI

DSP_INT0

DSP_INT1

DSP_INT2

DSP_INT3

X_INT0

X_INT1

X_INT2

X_INT3

X_DBINT

UART_INT

BOOT_INT

H_IRQ_PP

H_INT0

1

10

21

31

41

50

61

71

81

90

101

111

121

130

141

151

S_MPMC

DSP_DS#

DSP_PS#

DSP_IS#

DSP_IOSTRB#

DSP_MSTRB#

DSP_R/W#

DSP_DATA_DIR

DSP_DATA_OE

BSP0_SEL

BSP1_SEL

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

107

113

13

67

U

S

R

CY3712 8VP

CPL D

2

72

73

159

131

74

9

98

DSP_DATA_DIR

DSP_DATA_OE#

BSP0_SEL#

BSP1_SEL#

USR_SW0

USR_SW1

USR_SW2

USR_LED1

USR_LED2

USR_LED3

I

N

T

BDSP_DATA0

BDSP_DATA1

BDSP_DATA2

BDSP_DATA3

BDSP_DATA4

BDSP_DATA5

BDSP_DATA6

BDSP_DATA7

96

94

51

18

65

63

R

E

S

E

T

H_RST

VCC2_BAD

BRD_RST

SW_RST

DB_P_RST

DSP_RST

DB_RST

TBC_RST

MAN_RST

DA0

DA1

DA2

DA3

DA12

DA13

DA14

DA15

DA19

S_USER0

S_USER1

S_USER2

USER_LED1#

USER_LED2#

USER_LED3#

U19B

HOST

H_RDY

147

44

123

47

144

145

87

15

127

H_SRST

VCC2_BAD#

BRD_RST#

SW_RST#

DB_P_RST#

DSP_RST#

X_RESET#

TBC_RST#

MAN_RST#

85

84

146

5

52

45

136

56

34

BDSP_ADDR0

BDSP_ADDR1

BDSP_ADDR2

BDSP_ADDR3

BDSP_ADDR12

BDSP_ADDR13

BDSP_ADDR14

BDSP_ADDR15

BDSP_ADDR19

102

H_RDY

JTAG_EN

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

PP_A0

PP_A1

PP_A2

PP_A3

HA0

HA1

HA2

HA3

U19A

93

158

122

157

3.3V

FLOAT#

X_CNTL0

X_CNTL1

3.3V

R63

10K

R55

10K

R51

10K

R25

10K

JTAG_EN

X_STAT0

X_STAT1

DGND

R17

10K

R15

10K

R86

10K

R94

10K

X_INT0#

X_INT1#

X_INT2#

DB_DET#

X_INT3#

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

CPLD

Size

B

Date:

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

of

22

8.192 MHz OSCILLATOR

20.000 MHz OSCILLATOR

3.3V

5V

C65

C59

0.1uF

0.1uF

DGND

TS

DGND

L4

U23

1

VCC

1

R82

GND

OUT

L1

U21

HZ0805E601R

TS

VCC

GND

OUT

HZ0805E601R

33.2, 1%

MCLK1

EPSON 8.192MHz

R67 33.2, 1%

PP_SCLK

EPSON 20.000MHz

R83

DGND

R65

33.2, 1%

TBC_CLK

33.2, 1%

DGND

MCLK2

DAUGHTER BOARD CLOCK

3.3V

3.3V

R124

10K

R121

10K

R113

10K

U30

2

4

1

3

BRD_RST#

DSP_CLKOUT

12

10

13

11

7

R127

R119

1D

1PRE

1CLR

1CLK

1Q

2D

2PRE

2CLR

2CLK

2Q

GND

1Q

2Q

VCC

C87

X_CLKOUT

6

9

8

14

3.3V

SN74LVC74A

360

33.2, 1%

0.01uF

DGND

CLOCKS

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

of

22

DSP_DATA15

DSP_DATA14

DSP_DATA13

DSP_DATA12

DSP_DATA11

DSP_DATA10

DSP_DATA9

DSP_DATA8

DSP_DATA7

DSP_DATA6

DSP_DATA5

DSP_DATA4

DSP_DATA3

DSP_DATA2

DSP_DATA1

DSP_DATA0

DSP_ADDR22

DSP_ADDR21

DSP_ADDR20

DSP_ADDR19

DSP_ADDR18

DSP_ADDR17

DSP_ADDR16

DSP_ADDR15

DSP_ADDR14

DSP_ADDR13

DSP_ADDR12

DSP_ADDR11

DSP_ADDR10

DSP_ADDR9

DSP_ADDR8

DSP_ADDR7

DSP_ADDR6

DSP_ADDR5

DSP_ADDR4

DSP_ADDR3

DSP_ADDR2

DSP_ADDR1

DSP_ADDR0

2

143

110

109

108

107

105

11

10

9

8

7

5

141

140

139

138

137

136

134

133

132

131

DSP_ADDR[0..22]

123

122

121

119

118

117

116

115

114

113

104

103

102

101

100

99

DSP_DATA[0..15]

HPIENA

61

67

66

65

64

63

98

S_MPMC

32

DSP_BIO#

DSP_XF

31

27

IACK

INT3

INT2

INT1

INT0

NMI

RS

MP/MC

BIO

XF

I

N

T

/

R

S

T

M

C

B

S

P

S

1.8V

CLKOUT

CLKMD3

CLKMD2

CLKMD1

X2/CLKIN

X1

TOUT0

BCLKR1

BDR1

BFSR1

BCLKX1

BDX1

BFSX1

NC1

NC2

NC3

NC4

NC5

NC6

BCLKR0

BDR0

BFSR0

BCLKX0

BDX0

BFSX0

19

20

21

22

23

24

25

30

28

26

29

PS#

DS#

IS#

R/W#

MSTRB#

ISTRB#

HOLD#

R100

R105

R111

R120

R123

R129

33.2,

33.2,

33.2,

33.2,

33.2,

33.2,

X_RDY

DSP_PS#

DSP_DS#

DSP_IS#

DSP_R/W#

DSP_MSTRB#

DSP_IOSTRB#

1%

1%

1%

1%

1%

1%

X_MSC#

X_IAQ#

CLOCKOUT

94

79

78

77

97

96

82

R84

S_CLKMD3

S_CLKMD2

S_CLKMD1

33.2, 1%

Y2

CRYSTAL

DSP_CLKOUT

C70

22pF

C57

22pF

DSP_TOUT

DGND

42

47

44

49

60

54

DSP_BCLKR1

DSP_BDR1

DSP_BFSR1

DSP_BCLKX1

DSP_BDX1

DSP_BFSX1

38

35

36

71

74

73

41

45

43

48

59

53

DSP_BCLKR0

DSP_BDR0

DSP_BFSR0

DSP_BCLKX0

DSP_BDX0

DSP_BFSX0

POWER / GROUND

12

16

52

68

91

125

142

DSP_IACK#

DSP_INT3#

DSP_INT2#

DSP_INT1#

DSP_INT0#

DSP_NMI#

DSP_RST#

TMS320VC5402 PGE

READY

PS

DS

IS

R/W

MSTRB

IOSTRB

HOLD

HOLDA

MSC

IAQ

DVdd

DVdd

DVdd

DVdd

DVdd

DVdd

HAS#

H_R/W#

H_RDY

H_INT0#

HCNTL1

HCNTL0

HBIL

HCS

HDS2

HDS1

HAS

HR/W

HRDY

HINT/OUT1

HPIENA

H

P

I

U26

4

33

56

75

112

130

46

39

62

17

129

127

13

18

55

51

92

C

L

K

S

DVss

DVss

DVss

DVss

DVss

DVss

DVss

DVss

DVss

H_CNTL1

H_CNTL0

H_HWIL

H_CS0#

H_DS2#

H_DS#

HD7

HD6

HD5

HD4

HD3

HD2

HD1

HD0

14

40

57

72

76

93

106

128

144

6

135

124

120

95

81

69

58

J

T

A

G

CVss

CVss

CVss

CVss

CVss

CVss

CVss

CVss

CVss

CVss

H_AD7

H_AD6

H_AD5

H_AD4

H_AD3

H_AD2

H_AD1

H_AD0

EMIF

1

3

15

34

37

50

70

90

111

126

H_AD[0..7]

TCK

TDI

TDO

TMS

TRST

EMU0

EMU1/OFF

TEST1

CVdd

CVdd

CVdd

CVdd

CVdd

CVdd

CVdd

88

86

85

89

87

83

84

80

DSP_TCK

DSP_TDI

DSP_TDO

DSP_TMS

DSP_TRST#

DSP_EMU0

DSP_EMU1

NC/A22

NC/A21

NC/A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

3.3V

DGND

3.3V

3.3V

R68

10K

R93

10K

R99

10K

R76

10K

R73

10K

H_DS2#

HAS#

R143 10K

R142 10K

3.3V

R109 4.7K

DSP_INT3#

R118 4.7K

DSP_INT2#

DSP_EMU1

DSP_EMU0

Note:

Decoupling caps are shown on Page 19.

Note:

Crystal is ECS-200-20-18-TR.

HPIENA

HOLD#

R141 10K

R140 10K

R90

DSP_INT1#

10K

R102 10K

DSP_INT0#

DSP_RST#

X_RDY

TEXAS INSTRUMENTS INCORPORATED

DSP

Title

TMS320VC5402 DSK

DSP_BIO#

R139 10K

DSP_NMI#

Size

B

Date:

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

of

22

3.3V

C9

C17

C10

C15

0.1uF

0.1uF

0.1uF

0.1uF

DGND

DSP_ADDR[0..22]

C31

C38

C32

C46

0.1uF

0.1uF

0.1uF

DGND

DSP_DATA[0..15]

DGND U16

42

Vcc

31

Vcc

DSP_DATA0

DSP_DATA1

DSP_DATA2

DSP_DATA3

DSP_DATA4

DSP_DATA5

DSP_DATA6

DSP_DATA7

DSP_DATA8

DSP_DATA9

DSP_DATA10

DSP_DATA11

DSP_DATA12

DSP_DATA13

DSP_DATA14

DSP_DATA15

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

48

1

25

24

DSP_DATA_OE#

DSP_DATA_DIR

4

10

15

21

B

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

Vcc

Vcc

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

DGND

7

18

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

DGND

BDSP_DATA[0..15]

BDSP_DATA0

BDSP_DATA1

BDSP_DATA2

BDSP_DATA3

BDSP_DATA4

BDSP_DATA5

BDSP_DATA6

BDSP_DATA7

BDSP_DATA8

BDSP_DATA9

BDSP_DATA10

BDSP_DATA11

BDSP_DATA12

BDSP_DATA13

BDSP_DATA14

BDSP_DATA15

R18

360

DGND

7

18

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

4

10

15

21

28

34

Vcc

Vcc

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

3Y1

3Y2

3Y3

3Y4

4Y1

4Y2

4Y3

4Y4

GND

GND

GND

GND

GND

GND

DGND

BDSP_ADDR[0..22]

BDSP_ADDR0

BDSP_ADDR1

BDSP_ADDR2

BDSP_ADDR3

BDSP_ADDR4

BDSP_ADDR5

BDSP_ADDR6

BDSP_ADDR7

BDSP_ADDR8

BDSP_ADDR9

BDSP_ADDR10

BDSP_ADDR11

BDSP_ADDR12

BDSP_ADDR13

BDSP_ADDR14

BDSP_ADDR15

3.3V

DGND

R44

R45

R69

360

360

360

C37

C42

C30

C29

0.1uF

0.1uF

0.1uF

0.1uF

U15

DGND

DGND

GND

GND

GND

GND

Vcc

Vcc

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

3A1

3A2

3A3

3A4

4A1

4A2

4A3

4A4

1OE

2OE

3OE

4OE

GND

GND

SN74LVTH16244

1OE

1DIR

2OE

2DIR

GND

GND

GND

GND

U6

42

31

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

1

48

25

24

45

39

DSP_ADDR0

DSP_ADDR1

DSP_ADDR2

DSP_ADDR3

DSP_ADDR4

DSP_ADDR5

DSP_ADDR6

DSP_ADDR7

DSP_ADDR8

DSP_ADDR9

DSP_ADDR10

DSP_ADDR11

DSP_ADDR12

DSP_ADDR13

DSP_ADDR14

DSP_ADDR15

3.3V

0.1uF

DGND

DGND

DSP_ADDR16

DSP_ADDR17

DSP_ADDR18

DSP_ADDR19

DSP_ADDR20

DSP_ADDR21

DSP_ADDR22

28

34

39

45

SN74LVTH16245

DGND

R43

R42

R41

R40

R39

R38

R34

R35

R36

R37

360

360

360

360

360

360

360

360

360

360

42

31

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

1

48

25

24

45

39

Vcc

Vcc

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

3A1

3A2

3A3

3A4

4A1

4A2

4A3

4A4

1OE

2OE

3OE

4OE

GND

GND

Vcc

Vcc

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

3Y1

3Y2

3Y3

3Y4

4Y1

4Y2

4Y3

4Y4

GND

GND

GND

GND

GND

GND

7 DGND

18

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

4

10

15

21

28

34

DGND

BDSP_ADDR16

BDSP_ADDR17

BDSP_ADDR18

BDSP_ADDR19

BDSP_ADDR20

BDSP_ADDR21

BDSP_ADDR22

B

SN74LVTH16244

DGND

A

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

BUFFERS

Size

B

Date:

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

of

22

4.3V

3.3V

C2

U22A

14

0.1uF

R85

DSP_MSTRB#

U2

33.2, 1%

32_Y3

MEM_WE#

DSP_R/W#

VCC

SN74LVC32A

DGND

U22B

4

R81

32_Y4

2

3

5

6

11

10

14

13

DSP_ADDR15

DM_PG0

DSP_ADDR16

DM_PG1

DSP_ADDR17

DM_PG2

DSP_ADDR18

DM_PG3

33.2, 1%

1

15

DSP_PS#

MEM_RE#

8

SN74LVC32A

R9

3.3V

360

C

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

1A

2A

3A

4A

DGND

16

4

ADDR15

ADDR16

ADDR17

12

ADDR18

S

OE

GND

4.3V

SN74CBT3257

U29

1

2

3

NC

A

C1

VCC

Y

5

4

R110

04_Y

0.1uF

33.2, 1%

DGND

MEM_OE#

U1

GND

VCC

NC7SZ04M5

2

3

5

6

11

10

14

13

DSP_ADDR19

DM_PG4

DGND

DM_SEL#

1

15

8

R8

360

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

1A

2A

3A

4A

16

DGND

4

ADDR19

SRAM_BE#

9

12

S

OE

GND

SN74CBT3257

DGND

TEXAS INSTRUMENTS INCORPORATED

MEMORY DECODE

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

10

of

22

DSP_DATA[0..15]

DSP_ADDR[0..22]

D

BDSP_DATA[0..15]

3.3V

3.3V

BDSP_ADDR[0..22]

U4

ADDR19

ADDR18

ADDR17

ADDR16

ADDR15

9

16

17

48

1

2

3

4

5

6

7

8

18

19

20

21

22

23

24

25

BDSP_ADDR14

BDSP_ADDR13

BDSP_ADDR12

BDSP_ADDR11

BDSP_ADDR10

BDSP_ADDR9

BDSP_ADDR8

BDSP_ADDR7

BDSP_ADDR6

BDSP_ADDR5

BDSP_ADDR4

BDSP_ADDR3

BDSP_ADDR2

BDSP_ADDR1

BDSP_ADDR0

3.3V

47

26

28

11

12

FLASH_CE#

MEM_RE#

MEM_WE#

BRD_RST#

27

46

C6

C7

0.1uF

0.1uF

U5

DGND

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

VCC

DQ15/A-1

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

RY/BY

R12 10K

C5

0.1uF

BYTE

CE

OE

WE

RESET

NC1

NC2

NC3

DGND

DGND

37

45

43

41

39

36

34

32

30

44

42

40

38

35

33

31

29

ADDR17

ADDR16

ADDR15

BDSP_DATA15

BDSP_DATA14

BDSP_DATA13

BDSP_DATA12

BDSP_DATA11

BDSP_DATA10

BDSP_DATA9

BDSP_DATA8

BDSP_DATA7

BDSP_DATA6

BDSP_DATA5

BDSP_DATA4

BDSP_DATA3

BDSP_DATA2

BDSP_DATA1

BDSP_DATA0

DSP_ADDR14

DSP_ADDR13

DSP_ADDR12

DSP_ADDR11

DSP_ADDR10

DSP_ADDR9

DSP_ADDR8

DSP_ADDR7

DSP_ADDR6

DSP_ADDR5

DSP_ADDR4

DSP_ADDR3

DSP_ADDR2

DSP_ADDR1

DSP_ADDR0

15

10

13

14

23

22

18

19

20

21

24

25

26

27

42

43

44

1

2

3

4

5

SRAM_BE#

40

39

SRAM_CE#

MEM_WE#

MEM_RE#

6

17

41

28

VSS

VSS

NC/A17

NC/A16

VDD1

VDD2

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

I/O15

I/O14

I/O13

I/O12

I/O11

I/O10

I/O9

I/O8

I/O7

I/O6

I/O5

I/O4

I/O3

I/O2

I/O1

I/O0

UB

LB

CS

WE

OE

GND1

GND2

NC

11

33

DSP_DATA15

DSP_DATA14

DSP_DATA13

DSP_DATA12

DSP_DATA11

DSP_DATA10

DSP_DATA9

DSP_DATA8

DSP_DATA7

DSP_DATA6

DSP_DATA5

DSP_DATA4

DSP_DATA3

DSP_DATA2

DSP_DATA1

DSP_DATA0

38

37

36

35

32

31

30

29

16

15

14

13

10

9

8

7

12

34

AM29LV400B FLASH

64K x 16 SRAM

DGND

DGND

3.3V

R10 10K

FLASH_CE#

R3

SRAM_BE#

10K

MEMORY - FLASH & SRAM

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

11

of

22

5V

C4

BDSP_DATA[0..15]

UART_CE#

14

15

16

UART_RD#

UART_WR#

24

20

25

21

28

UART_INT

33

BRD_RST

39

VCC

SOUT

RTS

DTR

SIN

CTS

DSR

DCD

A2

A1

A0

RI

OUT1

OUT2

CS0

CS1

CS2

DDIS

TXRDY

RXRDY

RD1

WR1

XIN

RD2

WR2

XOUT

R5

360

360

22

R2

360

DGND

13

36

37

15

16

11

40

41

42

21

20

18

43

38

35

28

+

26

27

32

C18

ADS

BAUDOUT

INTRPT

RCLK

MR

NC1

NC2

NC3

NC4

VSS

R1OUT

R2OUT

R3OUT

R20

1M

C2+

C1-

C2-

27

+

5V

17

10

DGND

1.5K

C19

S_DCD

S_DSR

S_RXD

S_CTS

S_RI

V+

CT3

1uF

V-

R31

10K

13

14

C

8

9

11

S_RTS

S_TXD

S_DTR

1

+

22pF

Y1

3.6864 MHz

R1IN

R2IN

R3IN

C1+

18

19

FORCEON

FORCEOFF

INVALID

R1OUTB

5

6

7

10

12

CT4

1uF

25

R32

R4

44

GND

R23

10K

29

30

31

5V

T1OUT

T2OUT

T3OUT

T4OUT

T5OUT

CT1

1uF

3

4

CT2

R24

10K

BDSP_ADDR2

BDSP_ADDR1

BDSP_ADDR0

D7

D6

D5

D4

D3

D2

D1

D0

T1IN

T2IN

T3IN

T4IN

T5IN

VCC

5V

MAX3238

26

BDSP_ADDR[0..22]

9

8

7

6

5

4

3

2

24

23

22

19

17

BDSP_DATA7

BDSP_DATA6

BDSP_DATA5

BDSP_DATA4

BDSP_DATA3

BDSP_DATA2

BDSP_DATA1

BDSP_DATA0

U8

0.1uF

U3

1uF

C3

22pF

Crystal:

ECS-36-20-18-TR

0.1uF

DGND

1

12

23

34

TL16C550CFN

DGND

UART & RS232

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

12

of

22

C113

5VA

0.1uF

C114

C120

0.001uF, 500V

R136

10K

U37

~

G

2

U34

C106

R170

12M

0.250W

604K

DAA_TX+

U42

CPC5602C

R174

DAA_TX-

10M

R175

0.01uF

0.1uF

DAA_OH#

DAA_RING#

DAA_CID#

DAA_RX-

DAA_RX+

C91

0.1uF

C88

0.1uF

R131

BRTXF2

ZTX

ZNT

TXS

BRNTS

GAT

REF

DCS

IDC

ZDC

BRRPB

RXS

VDD

R146

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

150K

R165

C112

0.1uF

TIP

20

0.250W

U38

P3100SB

R137

100

R145 22.1

.063w

R149

R166

RING

1.6M

20

0.250W

R162402K

150K

CPC5600A

1

R168 806K

+ CT12

C93

0.01uF

R176

300

.063w

R158

.47uF

AGND

C82 220pF

R130

1M

F1

WICKMAN 3850500000

R144

C99

VCC

TXF1

TXTX+

TX

NC

GND

OH

RING

CID

RXRX+

SNP+

SNPRXF

RX

R156 200K

0.1uF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

0.1uF

C105

2000V

C83 220pF

2000V

604

R155806K

R134

.063w

1.5M

R135

B

1.5M

R169

12.1

JP4

TSW-102-07-G-S

Notes:

All resistors are 100W unless otherwise noted.

- means "Floating" Ground.

TEXAS INSTRUMENTS INCORPORATED

DATA ACCESS ARRANGEMENT

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

13

of

22

CT6

10uF

5VA

JP3

5VA

NON-AMPLIFIED

C62

AMPLIFIED

U20

R79

0.1uF

20.5K, 1%

GAIN

GAIN

1

2

3

SPEAKER_OUT

TSW-103-07-G-S

8

AGND

AGND

R77

VMID_AUDIO

INPUT -

BYPASS

INPUT +

VS

0

C60

20.5K, 1%

0.1uF

R80

+ CT8

0.1uF

3

OUTP2

20K

1uF

6

CT5

GND

VOUT

R78

C52

C51

R75

330uF

LM386

1K

0.047uF

AGND

R71

AGND

C

10

AGND

AGND

C72

100pF

C64

100pF

R89

R92

100K

5VA

8

100K

CT11

R106

MIC_IN

U25A

10K

R116

5.11K

5VA

R88

1uF

R104

TLC2272ACD

VMID_AUDIO

5

R98

1%

U25B

C121

0.1uF

10K

R103

100K

INP2

TLC2272ACD

C68

51.1K

1K

AGND

+

0.001uF

VMID_AUDIO

CT9

C122

10uF

0.1uF

INM2

AGND

TEXAS INSTRUMENTS INCORPORATED

SPEAKER / MICROPHONE

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

14

of

22

3.3V

5VA

C103

R167 0

3

4

DGND

DAA_RX+

5

6

DAA_RX-

18

MCLK1

20

FS1#

3.3V

15

BRD_RST#

R157 10K

R147 10K

R164 0

DGND

DIN1

22

16

14

12

10

8

26

C75

0.1uF

0.1uF

AGND

AUXP

DVDD

AUXM

AVDD(PLL)

AGND

C102

0.1uF

U39

R161 0

AVDD

5VA

AGND

9

7

D

25

INP

INM

OUTP

OUTM

23

DAA_TX+

24

DAA_TX-

MCLK

MONOUT

FS

FLAG

RESET

M/S

FSD

PWRDWN

SCLK

ALTDATA

FC

DOUT

DIN

DVSS

FILT

REFP

AVSS(PLL)

AVSS

REFM

27

13

21

19

SCLK1

17

FC1

11

DOUT1

28

C

C117

1

C115

0.1uF

2

0.1uF

TLC320AD50C

DGND

DGND

AGND

3.3V

5VA

C118

0.1uF

U31

R122 0

R117 0

AGND

INP2

3.3V

4

5

6

INM2

MCLK2

18

FS2#

20

BRD_RST#

15

R128 10K

R112 10K

R133 0

DGND

DIN2

22

16

14

12

10

8

26

DGND

AUXP

C101

0.1uF

0.1uF

AGND

DVDD

AVDD(PLL)

AUXM

5VA

C116

AVDD

AGND

9

7

25

INP

INM

OUTP

OUTM

23

24

R108

OUTP2

100

MCLK

C77

FS

MONOUT

FLAG

RESET

FSD

M/S

PWRDWN

SCLK

ALTDATA

FC

DIN

DOUT

DVSS

FILT

AVSS(PLL)

REFP

AVSS

REFM

27

0.01uF

13

21

AGND

19

SCLK2

17

FC2

11

DOUT2

28

1

C100

C74

0.1uF

0.1uF

TLC320AD50C

DGND

TEXAS INSTRUMENTS INCORPORATED

AGND

DGND

Title

TMS320VC5402 DSK

AUDIO CODECS

Size

B

Date:

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

15

of

22

4.3V

4.3V

C111

C110

0.1uF

0.1uF

U36

U35

VCC

2

3

5

6

11

10

14

13

SCLK1

X_CLKR0

X_CLKX0

FS1#

X_FSR0

X_FSX0

1

15

BSP0_SEL#

R150

VCC

DGND

16

2

3

5

6

11

10

14

13

DIN1

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

1A

2A

3A

4A

X_DX0

DSP_BCLKR0

DOUT1

X_DR0

DSP_BCLKX0

DSP_BFSR0

12

DSP_BFSX0

1

15

S

OE

R151

GND

360

360

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

1A

2A

3A

4A

16

DGND

4

DSP_BDX0

DSP_BDR0

9

12

S

OE

GND

SN74CBT3257

SN74CBT3257

C

DGND

DGND

4.3V

4.3V

C90

0.1uF

C92

0.1uF

DGND

U27

U28

VCC

2

3

5

6

11

10

14

13

SCLK2

X_CLKR1

X_CLKX1

FS2#

X_FSR1

X_FSX1

1

15

BSP1_SEL#

R125

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

1A

2A

3A

4A

16

VCC

DGND

4

2

3

5

6

11

10

14

13

DIN2

DSP_BCLKR1

X_DX1

DOUT2

DSP_BCLKX1

DSP_BFSR1

12

DSP_BFSX1

X_DR1

1

15

S

OE

R126

360

GND

360

SN74CBT3257

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

16

B

1A

2A

3A

4A

DSP_BDX1

DSP_BDR1

9

12

S

OE

GND

SN74CBT3257

DGND

DGND

TEXAS INSTRUMENTS INCORPORATED

Title

BSP MUX

TMS320VC5402 DSK

Size

B

Date:

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

16

of

22

3.3V

C49

C33

C34

C47

0.1uF

0.1uF

0.1uF

0.1uF

DGND U18

42

Vcc

31

Vcc

DGND

D

BDSP_DATA[0..15]

BDSP_DATA0

BDSP_DATA1

BDSP_DATA2

BDSP_DATA3

BDSP_DATA4

BDSP_DATA5

BDSP_DATA6

BDSP_DATA7

BDSP_DATA8

BDSP_DATA9

BDSP_DATA10

BDSP_DATA11

BDSP_DATA12

BDSP_DATA13

BDSP_DATA14

BDSP_DATA15

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

48

1

25

24

DATA2XD#

MEM_OE#

C

4

10

15

21

DGND

7

18

Vcc

Vcc

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

X_D0

X_D1

X_D2

X_D3

X_D4

X_D5

X_D6

X_D7

X_D8

X_D9

X_D10

X_D11

X_D12

X_D13

X_D14

X_D15

X_D[0..31]

C16

C12

C8

0.1uF

0.1uF

0.1uF

DGND

BDSP_ADDR[0..22]

1OE

1DIR

2OE

2DIR

GND

GND

GND

GND

C20

0.1uF

DGND

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

3.3V

DGND

42

31

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

1

48

25

24

45

39

BDSP_ADDR0

BDSP_ADDR1

BDSP_ADDR2

BDSP_ADDR3

BDSP_ADDR4

BDSP_ADDR5

BDSP_ADDR6

BDSP_ADDR7

BDSP_ADDR8

BDSP_ADDR9

BDSP_ADDR10

BDSP_ADDR11

BDSP_ADDR12

BDSP_ADDR13

BDSP_ADDR14

ADDR15

R46

28

34

39

45

GND

GND

GND

GND

U7

360

Vcc

Vcc

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

3A1

3A2

3A3

3A4

4A1

4A2

4A3

4A4

1OE

2OE

3OE

4OE

GND

GND

DGND

7

18

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

4

10

15

21

28

34

Vcc

Vcc

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

3Y1

3Y2

3Y3

3Y4

4Y1

4Y2

4Y3

4Y4

GND

GND

GND

GND

GND

GND

DGND

X_A[0..21]

X_A0

X_A1

X_A2

X_A3

X_A4

X_A5

X_A6

X_A7

X_A8

X_A9

X_A10

X_A11

X_A12

X_A13

X_A14

X_A15

SN74LVTH16244

SN74LVTH16245

3.3V

3.3V

DGND

DGND

C23

C13

0.1uF

C14

0.1uF

0.1uF

C27

C45

C41

C28

0.1uF

0.1uF

0.1uF

0.1uF

C24

0.1uF

U14

DGND

U10

DGND

7

22

BDSP_DATA0

BDSP_DATA1

BDSP_DATA2

BDSP_DATA3

BDSP_DATA4

BDSP_DATA5

BDSP_DATA6

BDSP_DATA7

BDSP_DATA8

BDSP_DATA9

BDSP_DATA10

BDSP_DATA11

BDSP_DATA12

BDSP_DATA13

BDSP_DATA14

BDSP_DATA15

5

6

8

9

10

12

13

14

15

16

17

19

20

21

23

24

DB_ABCE#

3

26

DB_ABLE#

2

27

DB_ABOE#

1

28

4

11

18

25

DGND

Vcc

Vcc

DGND

50

Vcc

35

Vcc

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

1CEAB

2CEAB

1CEBA

2CEBA

1LEAB

2LEAB

1LEBA

2LEBA

1OEAB

2OEAB

1OEBA

2OEBA

GND

GND

GND

GND

52

51

49

48

47

45

44

43

42

41

40

38

37

36

34

33

DGND

ADDR16

ADDR17

ADDR18

ADDR19

X_D16

X_D17

X_D18

X_D19

X_D20

X_D21

X_D22

X_D23

X_D24

X_D25

X_D26

X_D27

X_D28

X_D29

X_D30

X_D31

BDSP_ADDR20

BDSP_ADDR21

DSP_MSTRB#

MEM_RE#

MEM_WE#

MEM_OE#

DSP_XF

DSP_IOSTRB#

DSP_IACK#

DSP_TOUT

X_BIO#

3.3V

R72

54

31

DB_BACE#

55

30

DB_BALE#

56

29

DB_BAOE#

R50

360

DGND 42

31

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

1

48

25

24

45

39

Vcc

Vcc

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

3A1

3A2

3A3

3A4

4A1

4A2

4A3

4A4

1OE

2OE

3OE

4OE

GND

GND

7 DGND

18

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

4

10

15

21

28

34

Vcc

Vcc

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

3Y1

3Y2

3Y3

3Y4

4Y1

4Y2

4Y3

4Y4

GND

GND

GND

GND

GND

GND

X_A16

X_A17

X_A18

X_A19

X_A20

X_A21

X_MSTRB#

X_RE#

X_WE#

X_OE#

X_XF

X_IOSTRB#

X_IACK#

X_TOUT

DSP_BIO#

SN74LVTH16244

10K

DGND

A

32

39

46

53

GND

GND

GND

GND

TEXAS INSTRUMENTS INCORPORATED

Title

EXPANSION DB BUFFERS

SN74LVTH16543

TMS320VC5402 DSK

Size

B

DGND

Date:

5

DGND

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

17

of

22

X_A[0..21]

12V

12V#

5V

5V

J3A

5V

3.3V_DB

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

J3B

J9A

X_A11

X_A9

X_A7

X_A5

X_A3

X_A1

X_A21

X_D31

X_D29

X_D27

X_D25

X_D23

X_D21

X_D19

X_D17

X_D15

X_D13

X_D11

X_D9

X_D7

X_D5

X_D3

X_D1

X_RE#

X_OE#

X_MSTRB#

J9B

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

X_A18

X_A16

X_A14

X_A12

X_A10

X_A8

X_A6

X_A4

X_A2

X_A0

X_A20

X_D30

X_D28

X_D26

X_D24

X_D22

X_D20

X_D18

X_D16

X_D14

X_D12

X_D10

X_D8

X_D6

X_D4

X_D2

X_D0

X_WE#

X_RDY

X_DS#

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

X_CLKX0

X_FSX0

X_CLKR0

X_FSR0

X_CLKX1

X_FSX1

X_CLKR1

X_FSR1

X_TOUT

X_XF

X_INT0#

X_MSC#

X_RESET#

X_CNTL1

X_STAT1

X_INT2#

X_PS#

DB_DET#

SFM-140-L2-S-D-LC

SFM-140-L2-S-D-LC

3.3V_DB

3.3V_DB

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

X_A19

X_A17

X_A15

X_A13

5V

3.3V_DB

X_DX0

X_DR0

X_DX1

X_DR1

X_INT1#

X_BIO#

X_IACK#

X_IOSTRB#

X_IAQ#

X_DBINT#

X_CNTL0

X_STAT0

X_INT3#

X_IS#

X_CLKOUT

SFM-140-L2-S-D-LC

SFM-140-L2-S-D-LC

DGND

DGND

DGND

DGND

X_D[0..31]

MEMORY INT ERFACE

PERIPHERAL I NTERFACE

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

EXPANSION DB INTERFACES

Size

B

Date:

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

18

of

22

PUSHBUTTON RESET

3.3V

R159

SW2

1

2

4

3

10K

SW_RST#

KT11P2CM

DGND

PROCESSOR VOLTAGE SUPERVISOR

1.8V

R152

3.3V

20.5K, 1%

U40

1

MAN_RST#

4

C107

R163

0.1uF

56.2K, 1%

6

3

MR

VCC

PFI

RESET

NC

RESET

GND

PFO

2

7

BRD_RST#

BRD_RST

VCC2_BAD#

TPS3707-33D

DGND

RESET

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

19

of

22

USER LEDS

3.3V

DSP BOOT SOURCE SELECTION

USER OPTION DIP SWITCHES

3.3V

5

10

3.3V

D

R7

COM1

COM2

R171

150

RN3

10K

R1

R2

R3

R4

R5

R6

R7

R8

D5

745101272JTR

BOOT_INT#

HPI

DB

1

2

3

4

6

7

8

9

YELLOW

JP2

1

2

3

S_JTAGSEL

S_MPMC

S_CLKMD3

S_CLKMD2

TP1

USER_LED1#

TSW-103-07-G-S

S_CLKMD1

S_USER2

S_USER1

S_USER0

DGND

16

15

14

13

12

11

10

9

3.3V

SW1

R172

194-8MST

1

2

3

4

5

6

7

8

150

C

D6

YELLOW

Default Switch Settings (ON-OFF-OFF-ON-OFF-ON-OFF-OFF)

DGND

TP2

USER_LED2#

3.3V

R173

150

D7

YELLOW

TP3

USER_LED3#

LEDS/SWITCHES

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

20

of

22

3.3V DAUGHTERBOARD VOLTAGE

3257 VOLTAGE DIVIDER

EXTERNAL POWER PLUG

+5V & +5VA POWER

3.3V_DB

5V

4.3V

5V

5VA

J5

R138

DB_DET#

6

7

4

8

C104

3

1

2

9

10

0.1uF

1

HZ0805E601R

2

3.3V_DB

5

RASH 712

2.5 mm

10K

U33

5V

L2

D1

RESET

EN

OUT

OUT

IN

IN

NC

NC

NC

NC

FB/NC

GND

GND/HSINK

GND/HSINK

GND/HSINK

GND/HSINK

GND/HSINK

GND/HSINK

GND/HSINK

GND/HSINK

16

DB_P_RST#

C73

13

14

R52

MMBD4148

17

18

15

CT10

47uF

DGND

0.01uF

SWITCHCRAFT RASH712 PLUG

470

L3

+

11

12

19

20

CT16

HZ0805E601R

10uF

DGND

AGND

DGND

TPS76733Q

C

DGND

+3.3V & +1.8V DIGITAL VOLTAGE REGULATOR

5V

U41

DSP CORE & I/O DIFFERENTIAL VOLTAGE PROTECTION

CT17

47uF

3.3V

5

6

CT20

C119

10uF

0.1uF

3

1K

D3

DGND

10

R177

1

2

MMBD4148

C108

9

0.1uF

2

MMBD4148

D8

Green

MMBD4148

1OUT

1OUT

1FB/SENSE

DGND

DGND

23

24

25

R153

15.8K, 1%

1GND

2IN

2IN

2RESET

2EN

2OUT

2OUT

2SENSE

CT18

1K

1

2

7

8

13

14

10uF

22

3.3V

DGND

R148

3

150

1EN

1.8V

28

R154 30.1K, 1%

11

12

D2

1RESET

R178

1.8V

D4

1IN

1IN

17

18

19

+ CT19

10uF

2GND

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

15

16

20

21

26

27

CT15

47uF

DGND

DGND

TPS767D301

ALTERNATE EXTERNAL POWER

(DO NOT POPULATE)

5V

12V#

12V

J8

A

+5

GND

-12

+12

INPUT POWER

4

3

2

1

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

Size

B

Molex 15-24-4041

DGND

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

21

of

22

CPLD DECOUPLING CAPS

DSP DECOUPLING CAPS

For CVDD

For DVDD

3.3V

Pin

Pin

Pin

Pin

Pin

Pin

Pin

12

16

52

68

91

125

142

C21

0.01uF

Pin 40

C36

0.01uF

Pin 60

C22

0.01uF

Pin 62

C43

0.01uF

Pin 80

C35

0.01uF

Pin 100

C48

0.01uF

Pin 120

C61

0.01uF

10uF

Pin 140

C71

0.01uF

Pin 142

C66

0.01uF

Pin 160

C58

0.01uF

3.3V

C78

0.01uF

C96

0.01uF

C54

0.01uF

C56

0.01uF

C69

0.01uF

C76

0.01uF

C98

Pin

Pin

Pin

Pin

Pin

Pin

0.01uF

C63

4

33

56

75

112

130

Pin 20

1.8V

0.01uF

C53

0.01uF

C55

0.01uF

C86

0.01uF

C97

0.01uF

C89

0.01uF

CT13

+

CT14

10uF

DGND

DGND

CT7

10uF

DGND

GROUND TEST POINTS

CHASSIS GROUND

DAUGHTERBOARD STANDOFF GROUNDING

MT1

MH125-NP

MT2

MH125-NP

MT3

MT4

MH125-NP

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

MH125-NP

MT5

R1

0

DGND

DGND

DGND

DECOUPLING CAPS & GROUND

TEXAS INSTRUMENTS INCORPORATED

Title

TMS320VC5402 DSK

Size

B

Date:

5

Document Number

Rev

D600962

Wednesday, September 22, 1999

*

Sheet

1

22

of

22

Potrebbero piacerti anche

- Newnes Radio and Electronics Engineer's Pocket BookDa EverandNewnes Radio and Electronics Engineer's Pocket BookNessuna valutazione finora

- Toshiba Inventec Manaus 10AD Moterboard Notebook DiagramaDocumento43 pagineToshiba Inventec Manaus 10AD Moterboard Notebook Diagramaalbertec51Nessuna valutazione finora

- Newnes Radio and Electronics Engineer's Pocket Book: Revised by the Editorial Staff of Electronics Today InternationalDa EverandNewnes Radio and Electronics Engineer's Pocket Book: Revised by the Editorial Staff of Electronics Today InternationalNessuna valutazione finora

- Hawkboard Schematics v1Documento11 pagineHawkboard Schematics v1Sam KhawseNessuna valutazione finora

- HP Ze2000 - Quanta Ct8 - Rev 3bDocumento42 pagineHP Ze2000 - Quanta Ct8 - Rev 3bCarlos Alberto SalvadorNessuna valutazione finora

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- Gila EVT1 Schematic (.BakDocumento70 pagineGila EVT1 Schematic (.BakuimNessuna valutazione finora

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIDa EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINessuna valutazione finora

- SchematicDocumento8 pagineSchematicksajjNessuna valutazione finora

- HP Compaq Evo n620c - Inventec Fenway 3.0Documento53 pagineHP Compaq Evo n620c - Inventec Fenway 3.0Togorean MariaNessuna valutazione finora

- Pavilion ZD7000 NT1 QuantaDocumento35 paginePavilion ZD7000 NT1 QuantaMicu Adrian DanutNessuna valutazione finora

- Dsa Up LD 00006218Documento47 pagineDsa Up LD 00006218Hans PeterNessuna valutazione finora

- V.Govinda Rao M.tech-ICS 05024D1410Documento20 pagineV.Govinda Rao M.tech-ICS 05024D1410Kiran KumarNessuna valutazione finora

- Digitally Signed by FDSF DN: CN FDSF, o FSDFSD, Ou FFSDF, Email FDFSD@FSDFF, C US Date: 2009.10.17 12:36:05 +07'00'Documento82 pagineDigitally Signed by FDSF DN: CN FDSF, o FSDFSD, Ou FFSDF, Email FDFSD@FSDFF, C US Date: 2009.10.17 12:36:05 +07'00'João Luis N. Do AmaralNessuna valutazione finora

- Pioneer Deh 340, Deh 34, Deh 3400Documento37 paginePioneer Deh 340, Deh 34, Deh 3400Dan GuertinNessuna valutazione finora

- Toshiba L630 L635 Laptop SchematicDocumento56 pagineToshiba L630 L635 Laptop SchematicAgus Jhon80% (5)

- Acer - As9800 Model Cheela Odm Brand InventecDocumento71 pagineAcer - As9800 Model Cheela Odm Brand Inventeczack9mm2003Nessuna valutazione finora

- PowerBook G4 17" Low-ResDocumento45 paginePowerBook G4 17" Low-Resrabidz7Nessuna valutazione finora

- U3761mb TelefonoDocumento23 pagineU3761mb Telefonogabriel6276Nessuna valutazione finora

- Usbmod1: USB Plug and Play Serial Development ModuleDocumento5 pagineUsbmod1: USB Plug and Play Serial Development ModuleMaiChiVuNessuna valutazione finora

- Dact 0005Documento1 paginaDact 0005Lucas MaicáNessuna valutazione finora

- M1-EVT 051-6959 - 04000 Schematic BakDocumento1 paginaM1-EVT 051-6959 - 04000 Schematic Bakuim100% (1)

- Fujitsu p7230Documento68 pagineFujitsu p7230Nicu LiviuNessuna valutazione finora

- Ibm Thinkpad r30Documento36 pagineIbm Thinkpad r30dwayne_hibbertNessuna valutazione finora

- Swm3 Cpu Schematic PartslistDocumento4 pagineSwm3 Cpu Schematic PartslistAriel BecerraNessuna valutazione finora

- Patent Application Publication: (19) United StatesDocumento82 paginePatent Application Publication: (19) United StatesGek CagatanNessuna valutazione finora

- Apple M50 PVT.Documento67 pagineApple M50 PVT.Hgfdfgh KjhgjhkgNessuna valutazione finora

- Rome0 99Documento82 pagineRome0 99HUGO ROMERONessuna valutazione finora

- PIC-WEB-BOX, Board Revision C - PORT PINOUTDocumento1 paginaPIC-WEB-BOX, Board Revision C - PORT PINOUTalo 247Nessuna valutazione finora

- BK4811B Datasheet V1.2Documento37 pagineBK4811B Datasheet V1.2BradMorse50% (2)

- Tomtom One XL SchematicDocumento11 pagineTomtom One XL Schematicsuysuy00100% (1)

- Gigabyte Ga-M59sli-S5 - Rev 1.01Documento50 pagineGigabyte Ga-M59sli-S5 - Rev 1.01Rodrigo BarbosaNessuna valutazione finora

- LPC P2148Documento19 pagineLPC P2148Sharath Babu100% (1)

- RK3066 Mid PDFDocumento17 pagineRK3066 Mid PDFSharon MurphyNessuna valutazione finora

- P 3 NK 90 ZDocumento20 pagineP 3 NK 90 ZJairo PadronNessuna valutazione finora

- Hws 13642Documento3 pagineHws 13642dhieward100% (2)

- Usb RS232 422 485Documento1 paginaUsb RS232 422 485Uros SmiljanicNessuna valutazione finora

- Toshiba L510 6050A2303001-MB-A03Documento10 pagineToshiba L510 6050A2303001-MB-A03Valerică Hizanu100% (1)

- TOSHIBA Satellite L500 - INVENTEC PERUGIA 10MDocumento63 pagineTOSHIBA Satellite L500 - INVENTEC PERUGIA 10Mbiplab_kabiNessuna valutazione finora

- Ibm Rome3 (1) .5Documento83 pagineIbm Rome3 (1) .5حسن علي نوفلNessuna valutazione finora

- LB# 820-2347 Schematic Diagram (Project K50)Documento81 pagineLB# 820-2347 Schematic Diagram (Project K50)gmackp829100% (1)

- C640-C600 - 6050a2357502-Mb-A02-T1-Ct10Documento56 pagineC640-C600 - 6050a2357502-Mb-A02-T1-Ct10Gie Av100% (3)

- USBDM CF JMXXCLD V3Documento8 pagineUSBDM CF JMXXCLD V3Sergio Johann ComasNessuna valutazione finora

- Q16 051-6338-C.bakDocumento40 pagineQ16 051-6338-C.bakmarkbillupsNessuna valutazione finora

- GT Relay PanelDocumento53 pagineGT Relay PanelPamela Bradley100% (1)

- SL PM Changes-Additonal-Repeaters PDFDocumento12 pagineSL PM Changes-Additonal-Repeaters PDFrogmcarvalhoNessuna valutazione finora

- IBM Thinkpad T43 Laptop Schematics PDFDocumento88 pagineIBM Thinkpad T43 Laptop Schematics PDFDravmx Drav DravNessuna valutazione finora

- PowerBook G5Documento70 paginePowerBook G5whitejohnny71Nessuna valutazione finora

- Ovf20 CR: Repair Instructions ServiceDocumento7 pagineOvf20 CR: Repair Instructions ServiceMatti HynniNessuna valutazione finora

- 60528Documento23 pagine60528Andres CaminoNessuna valutazione finora

- q45 - rampAPPLE 台式G5线路图.bakDocumento74 pagineq45 - rampAPPLE 台式G5线路图.bakmarkbillupsNessuna valutazione finora

- PROF 7500 V31.2 DVB-S2 Tuner Receiver Box SchematicsDocumento3 paginePROF 7500 V31.2 DVB-S2 Tuner Receiver Box SchematicsavrelecNessuna valutazione finora

- Bl10ad - Adg-6050a2333201-Mb-A01 20100121Documento61 pagineBl10ad - Adg-6050a2333201-Mb-A01 20100121milanTT11100% (1)

- Samsung Gt-p3100 r0.6 SchematicsDocumento11 pagineSamsung Gt-p3100 r0.6 SchematicsWarren Donaldson100% (1)

- L1 - Q3. L3. L2.: Filter Not Needed On Soft Starter Circuit?Documento1 paginaL1 - Q3. L3. L2.: Filter Not Needed On Soft Starter Circuit?Konge Thethtunaung100% (1)

- Water LevelDocumento2 pagineWater LevelSujitha RaviNessuna valutazione finora

- IS42S16400Documento55 pagineIS42S164000106062007Nessuna valutazione finora

- Spru 031 FDocumento770 pagineSpru 031 F0106062007Nessuna valutazione finora

- 1 MetastabilityDocumento58 pagine1 Metastability0106062007Nessuna valutazione finora

- Digic Et4293 Exam AnswersDocumento6 pagineDigic Et4293 Exam Answers0106062007Nessuna valutazione finora

- Questions and AnswersDocumento199 pagineQuestions and AnswersRamesh100% (4)

- Wolfson WM8731 Audio CODECDocumento59 pagineWolfson WM8731 Audio CODECLeslie WrightNessuna valutazione finora

- SST 39 SF 010 ADocumento22 pagineSST 39 SF 010 A0106062007Nessuna valutazione finora

- VHDL TutorialDocumento264 pagineVHDL TutorialKishore SriNessuna valutazione finora

- DownloadDocumento14 pagineDownload0106062007Nessuna valutazione finora

- Intro To Quartus2Documento268 pagineIntro To Quartus20106062007Nessuna valutazione finora

- VILGADocumento2 pagineVILGA0106062007Nessuna valutazione finora

- Base SPB16.50.000 README-ReleaseInfoDocumento2 pagineBase SPB16.50.000 README-ReleaseInfo0106062007Nessuna valutazione finora

- Embed Lab7Documento6 pagineEmbed Lab7Seamap VietnamNessuna valutazione finora

- 81 gs3Documento122 pagine81 gs3Fernando Sebastian DiazNessuna valutazione finora

- (Ofdm-Thesis) Simulation of A Wireless MIMO System (2004)Documento73 pagine(Ofdm-Thesis) Simulation of A Wireless MIMO System (2004)Mohammed Ezzo100% (1)

- Iccv2011 StruckDocumento8 pagineIccv2011 Struck0106062007Nessuna valutazione finora

- Cvpr13 BenchmarkDocumento8 pagineCvpr13 Benchmark0106062007Nessuna valutazione finora