Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

LC4 Single Cycle Diagram

Caricato da

Adnaan Mukadam0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

547 visualizzazioni1 paginaSingle Cycle of Penn's LC4 computer

Copyright

© Attribution Non-Commercial (BY-NC)

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoSingle Cycle of Penn's LC4 computer

Copyright:

Attribution Non-Commercial (BY-NC)

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

547 visualizzazioni1 paginaLC4 Single Cycle Diagram

Caricato da

Adnaan MukadamSingle Cycle of Penn's LC4 computer

Copyright:

Attribution Non-Commercial (BY-NC)

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 1

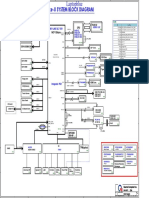

Single Cycle Implementation of the LC4 ISA

ALL CTL SIGNALS

Decode

ALU

Arith.CTL

regFile.WE I[8:6] 0x07 I[11:9] I[2:0] I[11:9]

rsMux.CTL

ArithMux.CTL

Arithmetic Ops

ALUMux.CTL

SEXT(I[4:0])

0 1 2

LOGIC.CTL

0 1 2

rs.addr

Register File

SEXT(I[5:0])

regInputMux.CTL

Logical Ops

0

RS[15:0]

rtMux.CTL

0 1

LogicMux.CTL

rt.adddr

SEXT(I[4:0])

1 0 1

SHIFT.CTL

DATA.WE

Shifter

PC

Instruction Address PC[15:0]

I[11:9]

Program Memory

rdMux.CTL

0

I[15:0]

rd.addr

Write Input

RT[15:0]

Data Address

2 0

Instruction

0x07

I[3:0]

CONST.CTL

Data Output

DATA Memory

Constants

3

I[8:0]

NZP.WE

CMP.CTL

I[11:9]

TEST

Data Input

NZP Register NZP Tester

PCMux.CTL

I[6:0]

0 0 1

Comparator

SEXT(I[8:0])

2 RS[15:0]

SEXT(I[10:0])

3 (0x8000 | UIMM8) 4

(PC & 0x8000) | (IMM11<<4)

I[7:0]

I[10:0]

Branch Unit

+1

PC+1

Potrebbero piacerti anche

- Processor Design Single Cycle Processor: Hung-Wei TsengDocumento20 pagineProcessor Design Single Cycle Processor: Hung-Wei Tsengwraith324Nessuna valutazione finora

- System Software Unit 1Documento23 pagineSystem Software Unit 1Hsejar CandyNessuna valutazione finora

- Basic Computer Organization and DesignDocumento35 pagineBasic Computer Organization and DesignVinay KumarNessuna valutazione finora

- ARM RTX Real-Time Operating SystemDocumento67 pagineARM RTX Real-Time Operating SystemLauren LoveNessuna valutazione finora

- 440 Datapath Control 1Documento25 pagine440 Datapath Control 1Srilatha PradeepNessuna valutazione finora

- Computer Architecture 3rd Edition by Moris Mano CH 05Documento35 pagineComputer Architecture 3rd Edition by Moris Mano CH 05Sadaf RasheedNessuna valutazione finora

- EE361 SingleMIPSDocumento19 pagineEE361 SingleMIPSThùyVũNessuna valutazione finora

- Computer Architecture MIPS Processor DescriptionDocumento41 pagineComputer Architecture MIPS Processor DescriptionAsif HussainNessuna valutazione finora

- cs2304 NolDocumento49 paginecs2304 NolAlex DavidNessuna valutazione finora

- Programmable Timing Functions Part 1: Timer-Generated InterruptsDocumento25 pagineProgrammable Timing Functions Part 1: Timer-Generated InterruptsBui Van PhatNessuna valutazione finora

- Module 01-MicrocontrollerDocumento15 pagineModule 01-MicrocontrollerRejwan TanzinNessuna valutazione finora

- Chapter 5 - The Processor: Datapath and ControlDocumento101 pagineChapter 5 - The Processor: Datapath and Controlapi-26072581Nessuna valutazione finora

- Arhitectura CalculatoarelorDocumento22 pagineArhitectura CalculatoarelormiryangelNessuna valutazione finora

- Datapaths II & Control IDocumento41 pagineDatapaths II & Control IAndrea AquinoNessuna valutazione finora

- M.Tech ES ARM LABDocumento14 pagineM.Tech ES ARM LABdownloadscribdpdfNessuna valutazione finora

- System Software Question Bank 2012 With Part-B AnswersDocumento49 pagineSystem Software Question Bank 2012 With Part-B Answerssumathi7975% (16)

- SSCD Module1Documento72 pagineSSCD Module1Chirag UNessuna valutazione finora

- Assignment3 2021HT80531Documento14 pagineAssignment3 2021HT80531crypto.investnmentNessuna valutazione finora

- CSC 5sem CS2304NOLDocumento60 pagineCSC 5sem CS2304NOLVinay Kshatriya HalNessuna valutazione finora

- Sic and SIC/XEDocumento14 pagineSic and SIC/XEravneet_mahal198100% (1)

- Basic Computer Organization and DesignDocumento35 pagineBasic Computer Organization and Designabhisrit2008Nessuna valutazione finora

- Chap. 5 Basic Computer Org. and Design: 5-1 Instruction CodesDocumento21 pagineChap. 5 Basic Computer Org. and Design: 5-1 Instruction CodesSisay ADNessuna valutazione finora

- Unit-1: Machine Architecture: This Chapter Gives YouDocumento14 pagineUnit-1: Machine Architecture: This Chapter Gives Yousridevi ramarajNessuna valutazione finora

- System ProgrammingDocumento21 pagineSystem Programmingatulsahu24Nessuna valutazione finora

- Cha 1Documento31 pagineCha 1Asha NaveenNessuna valutazione finora

- Asm AsmblerDocumento93 pagineAsm AsmblerstormviruxNessuna valutazione finora

- Cs/Coe 1541: Single and Multi-Cycle ImplementationsDocumento93 pagineCs/Coe 1541: Single and Multi-Cycle ImplementationsBobo JooNessuna valutazione finora

- System Software and Machine Architecture: Department of Computer Science National Tsing Hua UniversityDocumento31 pagineSystem Software and Machine Architecture: Department of Computer Science National Tsing Hua UniversitymonajosephjustinNessuna valutazione finora

- CHAPTER 5, Inside Digital DesignDocumento33 pagineCHAPTER 5, Inside Digital DesignSyed Abdullah RizviNessuna valutazione finora

- Module 1Documento72 pagineModule 1H3ck AssassinNessuna valutazione finora

- Introduction To Free-RTOS: Deepak D'SouzaDocumento34 pagineIntroduction To Free-RTOS: Deepak D'SouzaNguyễn QuânNessuna valutazione finora

- System Software NotesDocumento104 pagineSystem Software NotesVishal PatelNessuna valutazione finora

- Design Contest 2010 MentorDocumento27 pagineDesign Contest 2010 MentorUjjwal KantNessuna valutazione finora

- Systemsoftwarenotes 100929171256 Phpapp02Documento201 pagineSystemsoftwarenotes 100929171256 Phpapp02Shruthi PatilNessuna valutazione finora

- Control UnitDocumento67 pagineControl UnitnitinmgNessuna valutazione finora

- SsnotesDocumento89 pagineSsnoteskavirajeeNessuna valutazione finora

- System Software: An Introduction To Systems Programming Leland L. Beck 3rd Edition Addison-Wesley, 1997Documento40 pagineSystem Software: An Introduction To Systems Programming Leland L. Beck 3rd Edition Addison-Wesley, 1997Shoyab Ahamed50% (4)

- ECE 5570 Design of Reconfigurable Digital Machines Design of 16 Bit RISC ProcessorDocumento11 pagineECE 5570 Design of Reconfigurable Digital Machines Design of 16 Bit RISC Processorpitler999Nessuna valutazione finora

- System Software Notes 5TH Sem VtuDocumento15 pagineSystem Software Notes 5TH Sem VtuNeha Chinni100% (5)

- Computer Architecture: CSCE 350Documento41 pagineComputer Architecture: CSCE 350kherberosNessuna valutazione finora

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDa EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNessuna valutazione finora

- RISC Processor DesignDocumento33 pagineRISC Processor Designkomal iqbalNessuna valutazione finora

- Fundamentals of Processor Design: Using Figures From by Hamblen and FurmanDocumento35 pagineFundamentals of Processor Design: Using Figures From by Hamblen and Furmanwilliamjamir2295Nessuna valutazione finora

- Embedded Systems Lab ManualDocumento60 pagineEmbedded Systems Lab Manualtmuthu123100% (1)

- Project1 1Documento18 pagineProject1 1Bharath KumarNessuna valutazione finora

- Project1 1Documento18 pagineProject1 1Bharath KumarNessuna valutazione finora

- Central Processing Unit (CPU) : TopicDocumento6 pagineCentral Processing Unit (CPU) : TopicGaurav KulkarniNessuna valutazione finora

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCDa EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNessuna valutazione finora

- Hapter Outline: Cpu Memory Input and Output UnitDocumento34 pagineHapter Outline: Cpu Memory Input and Output UnittoswaroopNessuna valutazione finora

- Exercises Lg1 Lg6Documento4 pagineExercises Lg1 Lg6Helga PravinNessuna valutazione finora

- Mit Ocw Complex Digital Systems Lab1Documento6 pagineMit Ocw Complex Digital Systems Lab1Monika YadavNessuna valutazione finora

- Pic16f FeaturesDocumento40 paginePic16f Featuresveeramaniks408Nessuna valutazione finora

- 60 Years Ago and Now: ISE1 / EE2 Principles of Computers What Will You Be Learning?Documento18 pagine60 Years Ago and Now: ISE1 / EE2 Principles of Computers What Will You Be Learning?osmanatam1Nessuna valutazione finora

- CS2304 System Software UNIT I NOTESDocumento9 pagineCS2304 System Software UNIT I NOTESClashing with DeepakNessuna valutazione finora

- SsDocumento60 pagineSsponns100% (1)

- A Brief History of Micro ProgrammingDocumento17 pagineA Brief History of Micro Programmingmehima10Nessuna valutazione finora

- Basic Computer OrganizationDocumento19 pagineBasic Computer OrganizationBarikly RobbyNessuna valutazione finora

- Programmable Timing Functions Part 1: Timer-Generated InterruptsDocumento26 pagineProgrammable Timing Functions Part 1: Timer-Generated InterruptsRavi KanthNessuna valutazione finora

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesDa EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNessuna valutazione finora

- A Tutorial Introduction To The Lambda CalculusDocumento9 pagineA Tutorial Introduction To The Lambda CalculusDevon LePageNessuna valutazione finora

- Proving ThingsDocumento215 pagineProving ThingsAdnaan MukadamNessuna valutazione finora

- Robinson CL2000 PDFDocumento24 pagineRobinson CL2000 PDFAdnaan MukadamNessuna valutazione finora

- CIS 380 Notes: September 11, 2014Documento1 paginaCIS 380 Notes: September 11, 2014Adnaan MukadamNessuna valutazione finora

- Proving ThingsDocumento215 pagineProving ThingsAdnaan MukadamNessuna valutazione finora

- 360CH2Documento6 pagine360CH2Adnaan MukadamNessuna valutazione finora

- PrometheusDocumento2 paginePrometheusAdnaan MukadamNessuna valutazione finora

- Groups and Symmetry A Guide To Discovering MathematicsDocumento112 pagineGroups and Symmetry A Guide To Discovering MathematicsAdnaan Mukadam100% (1)

- Watch Size GuideDocumento4 pagineWatch Size GuideAdnaan MukadamNessuna valutazione finora

- Math 410Documento1 paginaMath 410Adnaan MukadamNessuna valutazione finora

- Parameterizing Curves SurfacesDocumento3 pagineParameterizing Curves SurfacesAdnaan MukadamNessuna valutazione finora

- Introduction To Non Parametric Statistical Methods Research GateDocumento46 pagineIntroduction To Non Parametric Statistical Methods Research GateAaron FuchsNessuna valutazione finora

- P2P Technology User's ManualDocumento8 pagineP2P Technology User's ManualElenilto Oliveira de AlmeidaNessuna valutazione finora

- A320LEAP1A-B12-0008.5 Cont&Ind R1 220517Documento78 pagineA320LEAP1A-B12-0008.5 Cont&Ind R1 220517simsimsomNessuna valutazione finora

- Help Where Can You Get Free Ebook For 8086 Microprocessor by A K Roy and K N Bhurchandi or by Kenneth AyalaDocumento3 pagineHelp Where Can You Get Free Ebook For 8086 Microprocessor by A K Roy and K N Bhurchandi or by Kenneth AyalaasuhassNessuna valutazione finora

- ZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFDocumento48 pagineZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFSebastian StanacheNessuna valutazione finora

- Detailed List and Syllabuses of Courses: Syrian Arab Republic Damascus UniversityDocumento10 pagineDetailed List and Syllabuses of Courses: Syrian Arab Republic Damascus UniversitySedra MerkhanNessuna valutazione finora

- Mil Module 5Documento39 pagineMil Module 5anthony70% (20)

- Anti Lock Brake SystemDocumento41 pagineAnti Lock Brake SystemToua YajNessuna valutazione finora

- Review of DC-DC Converters in Photovoltaic Systems For MPPT SystemsDocumento5 pagineReview of DC-DC Converters in Photovoltaic Systems For MPPT SystemsLuis Angel Garcia ReyesNessuna valutazione finora

- Appendix B: Technical InformationDocumento11 pagineAppendix B: Technical InformationOnTa OnTa60% (5)

- Presentation SLTDocumento14 paginePresentation SLTAliNessuna valutazione finora

- Poly Matla BBDocumento2 paginePoly Matla BBdandiNessuna valutazione finora

- Awa Se E Dura GiyaDocumento6 pagineAwa Se E Dura GiyaChathura KumaraNessuna valutazione finora

- Free PDF Reader Sony Ericsson w595Documento2 pagineFree PDF Reader Sony Ericsson w595AdamNessuna valutazione finora

- Controller, Asst - Controller, SR - Accountant, Accounting ManagerDocumento3 pagineController, Asst - Controller, SR - Accountant, Accounting Managerapi-72678201Nessuna valutazione finora

- Wayne Patterson, Cynthia E. Winston-Proctor - Behavioral Cybersecurity - Applications of Personality Psychology and Computer Science (2019, Taylor & Francis - CRC) - Libgen - LiDocumento291 pagineWayne Patterson, Cynthia E. Winston-Proctor - Behavioral Cybersecurity - Applications of Personality Psychology and Computer Science (2019, Taylor & Francis - CRC) - Libgen - Lisor ronNessuna valutazione finora

- Oil and Gas Reloaded: Offshore ArgentinaDocumento9 pagineOil and Gas Reloaded: Offshore ArgentinaMuhammad Fahmi AnbNessuna valutazione finora

- An 0591 enDocumento9 pagineAn 0591 enSửaĐồĐiệnNessuna valutazione finora

- ROZEE CV 219 Adnan KhanDocumento4 pagineROZEE CV 219 Adnan KhanMaria JavedNessuna valutazione finora

- HP Client Management Interface Technical WhitepaperDocumento39 pagineHP Client Management Interface Technical Whitepaperpottytoddy1422Nessuna valutazione finora

- Tommy Molina ResumeDocumento2 pagineTommy Molina Resumeapi-266666163Nessuna valutazione finora

- Computer and Network Security: Dan Boneh and John MitchellDocumento60 pagineComputer and Network Security: Dan Boneh and John Mitchell19001015049 ROHITNessuna valutazione finora

- Using Visio PDFDocumento12 pagineUsing Visio PDFAnonymous Af4ORJNessuna valutazione finora

- Red Hat Enterprise Linux-6-6.8 Release Notes-En-UsDocumento65 pagineRed Hat Enterprise Linux-6-6.8 Release Notes-En-Uskamel najjarNessuna valutazione finora

- Block Diagram and Signal Flow GraphDocumento15 pagineBlock Diagram and Signal Flow GraphAngelus Vincent GuilalasNessuna valutazione finora

- Pacific General ManualDocumento53 paginePacific General Manualroi_marketingNessuna valutazione finora

- IDC - China's Public Cloud Service Market Tops US$5.4 Billion in 1H 2019 As Competition IntensifiesDocumento7 pagineIDC - China's Public Cloud Service Market Tops US$5.4 Billion in 1H 2019 As Competition IntensifiesJ. BangjakNessuna valutazione finora

- Management Reporter Integration Guide For Microsoft Dynamics® AX - DynAXDataProvInstGuide - ENUSDocumento17 pagineManagement Reporter Integration Guide For Microsoft Dynamics® AX - DynAXDataProvInstGuide - ENUSUmesh PanditNessuna valutazione finora

- CRT Learning Module: Course Code Course Title No. of Hours Module TitleDocumento16 pagineCRT Learning Module: Course Code Course Title No. of Hours Module TitleEiszel CadacioNessuna valutazione finora

- Case Study Problem StatementDocumento2 pagineCase Study Problem StatementSahil GargNessuna valutazione finora