Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

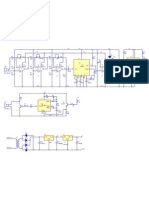

IO Door Board Schematic

Caricato da

villa1960Descrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

IO Door Board Schematic

Caricato da

villa1960Copyright:

Formati disponibili

INPUT/OUTPUT, DOOR, BOARD SCHEMATIC

4 3 2 1

754-278-11

REV A

PAGE 1 OF 2

REVISIONS

REV ECO

EA EB A 4451

DESCRIPTION

PROTOTYPE RELEASE RE-ROUTED R87-90 & FIXED 4001 PART & change J40 PRODUCTION RELEASE

BY/DATE CHK/DATE

TDW/04MAY98 TDW/02JUN98 TDW/22JULY98

NOTES:

(UNLESS OTHERWISE SPECIFIED)

1) ALL SURFACE MOUNT RESISTORS EXPRESSED IN OHMS 63mW 5% 2) ALL CAPACITORS EXPRESSED IN MICROFARADS 3) ALL 14 PIN ICS, PIN 14 IS PWR, PIN 7 IS GND. ALL 16 PIN ICS, PIN 16 IS PWR, PIN 8 IS GND. ALL 20 PIN ICS, PIN 20 IS PWR, PIN 10 IS GND. ALL 32 PIN ICS, PIN 32 IS PWR, PIN 16 IS GND.

+13VDC

D

J41 1A 1B 1C 2A 2B 2C 3A 3B 3C 4A 4B 4C 5A 5B 5C 6A 6B 6C 7A 7B 7C 8A 8B 8C 9A 9B 9C 10A 10B 10C 11A 11B 11C 12A 12B 12C 13A 13B 13C 14A 14B 14C 15A 15B 15C 16A 16B 16C 17A 17B 17C 18A 18B 18C 19A 19B 19C 20A 20B 20C 21A 21B 21C 22A 22B 22C 23A 23B 23C 24A 24B 24C 25A 25B 25C 26A 26B 26C 27A 27B 27C 28A 28B 28C 29A 29B 29C 30A 30B 30C 31A 31B 31C 32A 32B 32C

FUNCTIONALITY FOR DIFFERENT ADDRESSES (When a Bx is zero, it's LED will light)

STRAPPING B3 B2 B1 B0 ADDRESS J41 pin 1C 3C 5C 7C 9C 11C 13C 15C 17C 19C 21C 23C 25C 27C 29C 31C 2C 4C 6C 8C 10C 12C 14C 16C 18C 20C 22C 24C 26C 28C 30C 32C 1C 3C 5C 7C 9C 11C 13C 15C 17C 19C 21C 23C 25C 27C 29C 31C 2C 4C 6C 8C 10C 12C 14C 16C 18C 20C 22C 24C 26C 28C 30C 32C NET IN0 IN1 IN2 IN3 IN4 IN5 IN6 IN7 IN8 IN9 IN10 IN11 IN12 IN13 IN14 IN15 OUT0 OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 OUT8 OUT9 OUT10 OUT11 OUT12 OUT13 OUT14 OUT15 IN0 IN1 IN2 IN3 IN4 IN5 IN6 IN7 IN8 IN9 IN10 IN11 IN12 IN13 IN14 IN15 OUT0 OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 OUT8 OUT9 OUT10 OUT11 OUT12 OUT13 OUT14 OUT15 FUNCTION HOLD1 HOLD2 HOLD3 HOLD4 HOLD5 CHANGE DEAL CASH OUT BET MAX BET ONE COIN IN 1 COIN IN 2 COIN IN 3 COIN IN 4 COIN IN 5 COIN IN 6 HOLD 1 LIGHT HOLD 2 LIGHT HOLD 3 LIGHT HOLD 4 LIGHT HOLD 5 LIGHT CHANGE LIGHT DEAL LIGHT CASH OUT LIGHT BET MAX LIGHT BET ONE LIGHT LOCK OUT SOLENOID DIVERTER SOLENOID DENOM LAMP INSERT COIN COIN ACCEPTED GAME OVER DOOR ID 0 DOOR ID 1 DOOR ID 2 DOOR ID 3 SERV REQ DOUBLE UP DIVERTER DET 1 DIVERTER DET 2 PLAY 1 COIN PLAY 2 COINS PLAY 3 COINS PLAY 4 COINS PLAY 5 COINS UNUSED UNUSED UNUSED FEATURE 1 LIGHT FEATURE 2 LIGHT FEATURE 3 LIGHT FEATURE 4 LIGHT SERV REQ LIGHT DOUBLE UP LIGHT DIVERTER 2 DIVERTER 3 PAYLINE 1 LAMP PAYLINE 2 LAMP PAYLINE 3 LAMP PAYLINE 4 LAMP PAYLINE 5 LAMP PAYLINE 6 LAMP PAYLINE 7 LAMP PAYLINE 8 LAMP I/O

IN0

OUT0

IN1

TP

28020028H

OUT1

TP

BGND OUT2 BGND IN3 +25VDC OUT3

2802002AH

+25VDC +25VDC BGND AGND SENGND SENCLK SDATA_ADR SDATA_RXA SDATA_TXA SDATA_TXB SENSTB SENRST\ J40

IN4 +25VDC OUT4 +25VDC IN5 SENCLK OUT5 SDATA ADR IN6

TP

B3 B2 B1 B0 1 0 1 0

INPUTS

IN2

28020068H

OUT6 14 13 12 11 10 9 8 7 6 5 4 3 2 1

TP TP

+13VDC SDATA TXA AGND BGND +25VDC +13VDC SENRST\ (SD2) SENSTB (SD3) SDATA TXB (SD5) SDATA TXA (SD0) SDATA RXA (SDO) SDATA ADR (SD4) SENCLK (SD1) SENGND IN7 SDATA TXB OUT7 SD2 SD3 SD5 SD0 SD4 SD1 IOEN STRB C2SDO C1SDO C1SDI MUX/ADR SCLK SENSTB IN8 SENRST\ OUT8 Main Circuitry

TP

POWER

2802006AH

SENET DATA

OUTPUTS

DWG NO:

IN9 PGND OUT[15..0] OUT[15..0] OUT9 AGND AGND IN[15..0] IN10 AGND B[0..3] B[0..3] OUT10 AGND IN11 Main Circuitry OUT11 B1 IN12 AGND OUT12 B2 IN13 AGND 1 1 1 1 OUT13 + C1 IN14 .01uF 50V 3.3uF 35V .01uF 50V 1 10uF 16V OUT14 B3 R1 0 OHM 3Amps 2 OUT15 IN15 AGND 2 2 2 2

TP TP

14 PIN Through Hole, Right Angle, Mini-Fit

754 278 11

B0

2802002CH HARNESS STRAP FOR B0 ( 20B-21A )

IN[15..0] SD[5..0] SDOUT SD[5..0] SDOUT

INPUTS

SENGND

2802002EH

HARNESS STRAP FOR B1 ( 25B-26B )

B3 B2 B1 B0 1 0 1 1

HARNESS STRAP FOR B2 ( 27B-28B ) 2802006CH

C6

+ C5

C29

SDATA RXA

HARNESS STRAP FOR B3 ( 31B-32B ) 2802006EH

PGND

96 pin 3 row DIN

PGND

OUTPUTS

ALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OF INTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THIS INFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TO BE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATED BY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESS CONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENT COVENANTS IT WILL NOT BE USED IN ANY MANNER DETRIMENTAL TO THE INTEREST OF IGT, AND MUST BE RETURNED ON DEMAND.

DRAWN

DATE

INTERNATIONAL GAME TECHNOLOGY

9295 PROTOTYPE DRIVE RENO, NV 89511

TITLE

SCHEMATIC PCB, 960 MULTI I/O

DWG. NO. REV LTR

DWG. SIZE

C

APPROVED

754 278 11

DATE

A

1 OF __ 2 SHT __

CHECKED

DATE

SCALE

T.D.WAXMAN

04MAY98

NONE

AUGUST 24, 2001

ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY)

INPUT/OUTPUT, DOOR, BOARD SCHEMATIC

754-278-11

REV A

PAGE 2 OF 2

VDD 1 1 1 1 1 1 1 1 R86 2.2K 2 2 R87 2.2K R59 1 R60 1 R61 1 R62 1 R63 1 R65 1 R66 1 R69 1 R70 1 R72 1 R75 1 R76 1 R77 1 R78 1 R46 1 R79 1 1 1 1 1 1 1 1 1M O1 O2 O3 O4 O5 O6 2 1M 2 1M 2 1M 2 2 3 5 7 9 11 13 1M 1M 2 1M 2 1M 2 1M 2 1M 2 1M 2 1M 2 1M 2 IBIT7 IBIT6 IBIT5 IBIT4 IBIT3 IBIT2 IBIT1 IBIT0 1 9 10 1 15 14 13 4 5 6 7 11 1M 2 1M 2 1M 2 IBIT15 IBIT14 IBIT13 IBIT12 IBIT11 IBIT10 IBIT9 IBIT8 1 15 14 13 4 5 6 7 11 9 10

R80 2.2K IN[15..0] 2 2

R81 2.2K 2

R82 2.2K 2

R83 2.2K 2

R84 2.2K 2

R85 2.2K

U5 P/S CLK H G F E D C B A SER 4021 QH QG QF 3 12 2 1 1 1 1 Q9 1 2 3 4 S1 G1 S2 G2 D1 D1 D2 D2 8 7 6 5 1 RT16 1 1 1 1 RT8

IN15 IN14 IN13 IN12 IN11 IN10 IN9 IN8 IN7 IN6 IN5 IN4 IN3 IN2 IN1 IN0 1

t

2

OUT0

OUT[15..0]

TP TP

R54 100K 2 2

R53 100K 2

R58 100K 2

R57 100K 1 1 R55 R56 R51 1 1 1 1 R42 1 R43 1M 2 1M 2 R52 R47 R48 1M 1M 2 1M 1M 2 1M 2 1M 2 2 2

C27 .01uF

C28 .01uF

C25 .01uF

C26 .01uF

OUT1

U9 1 2 3 15 STR D CLK OE Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 QS QS 4094 4 5 6 7 14 13 12 11 9 10 OBIT0 OBIT1 OBIT2 OBIT3 OBIT4 OBIT5 OBIT6 OBIT7

1 2 3 4

DUAL N CHANNEL FET Q8 S1 D1 8 7 G1 D1 6 S2 D2 5 G2 D2 DUAL N CHANNEL FET Q7 S1 D1 8 7 G1 D1 6 S2 D2 5 G2 D2 DUAL N CHANNEL FET Q6 S1 D1 8 7 G1 D1 6 S2 D2 5 G2 D2 DUAL N CHANNEL FET Q5

RT7

t

1 RT15 2

OUT2

t

1 2 RT6

OUT3

U10 P/S CLK H G F E D C B A SER 4021 R23 2.2K 2 QH QG QF 3 12 2

t

1 RT14 2

1 2 3 4

OUT4

t

1 2 RT5

OUT5

TP TP

TP

1 1 1 1 1

C22 .01uF

C21 .01uF

C24 .01uF

C23 .01uF

t

1 RT13 2

R49 100K 2 2

R50 100K 2

R45 100K 2

R44 100K

1 2 3 4

OUT6

t

1 2

OUT7 +13VDC

RT4

t

8 7 6 5 1 RT12 2

U8 4503

R35 100K 2 2

R34 100K 2

R41 100K 2

R40 100K 1 1 R38 R39 R32 R33 R28 R29 R24 R26 1M 1M 2 1M 2 1M 2 1M 2 1M 2 1M 2 1M 2 2

C19 .01uF

C20 .01uF

C17 .01uF

C18 .01uF

1 2 3 4

S1 G1 S2 G2

D1 D1 D2 D2

1 R64 4.7K 2

OUT8

OUT9

2 4 6 10 12 14

1 15

R95 2.2K

R94 2.2K 2 2

R93 2.2K 2

R92 2.2K 2

R91 2.2K 2

R90 2.2K 2

R89 2.2K 2

C

SD[5..0]

R88 2.2K VDD

U4 1 2 3 15 STR D CLK OE Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 QS QS 4094 4 5 6 7 14 13 12 11 9 10 OBIT8 OBIT9 OBIT10 OBIT11 OBIT12 OBIT13 OBIT14 OBIT15

TP TP

1 1 1 1 1 1 1 1 1 1

1 2 3 4

DUAL N CHANNEL FET Q4 S1 D1 8 7 G1 D1 6 S2 D2 5 G2 D2 DUAL N CHANNEL FET Q3 S1 D1 8 7 G1 D1 S2 D2 6 5 G2 D2 DUAL N CHANNEL FET Q2 S1 D1 8 G1 D1 7 6 S2 D2 5 G2 D2 DUAL N CHANNEL FET

DA DB

I1 I2 I3 I4 I5 I6

RT3

t

1 RT11 1 2 2

OUT10

C

OUT11 2 OUT12

U7A SD0 1 2 40106 U7B SD1 3 4 40106 U7C SD2 5 6 40106 U7D IOEN SCLK C1SDO

RT10 1 RT2

1 2 3 4

t

1 2 RT9

t t

1 RT1 2

OUT13

C14 .01uF

C13 .01uF

C16 .01uF

C15 .01uF

U6B 4 4001

5 2 6

R30 100K 2

R31 100K 2

R25 100K 2

R27 100K

1 2 3 4

OUT14

t

1 2

OUT15

DWG NO:

PGND SD3 9 8 40106 4021EN U7E SD4 11 10 40106 9 U3 VDD SD5 E2 VDD SHUNT 1 R22 2.2K E1 PADS 2 U2 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 QS QS 4094 1 1 1 1 1 1 4 5 6 7 14 13 12 11 9 10 10 7 2 15 11 9 1 14 4 6 5 A0 A1 A2 A3 B0 B1 B2 B3 A>B (i) A=B (i) A<B (i) 4585 13 OPTIONAL RESISTORS (VALUE = 2.2K) INSTALLED ON BOTTOM SIDE OF BOARD 1 R13 2 R7 10K 2 2 10K 2 2 10K 2 2 10K 2 2 1 R20 2 680 .25W 1 1 1 R19 2 680 .25W 1 R18 2 680 .25W DS1 to DS4 and R17 to R20 are OPTIONAL 12 13 4001 11

TP

STRB CH1SDI

754 278 11

MUX/ADR 8

U6C 4001 10 R21 2.2K 8 U1B Q 13

TP

1 2 3 15

TP TP TP

D CLK

STR D CLK OE

B

U6A 6 U1A Q 1 1 2 4001 3 1 2 3 4 Q1 S1 G1 S2 G2 D1 D1 D2 D2 8 7 6 5 R5 1

TP

9 11 A<B (o) A=B (o) A>B (o) 12 3 13

TP

2 27

SDOUT

TP TP

12 4013

5 3

D CLK

TP

VDD U7F 12 40106

10

DUAL N CHANNEL FET Q R 2 4013 4

TP

R6 10K 2 2

R73 10K 2

R68 10K 2

R67 10K 2

R74 10K 2

R71 1K .125W

1 DS1 R8

R17

2 2 2 R12 2.2K 2 2

680 .25W 1 1 B[0..3] 1 1 R15 2 R9 R14 2

1 DS2

1 DS3 R10

U6D

1 1 R16 1 2 3 4 +13VDC R11 1 10 0.1W 2 1 1 1 1 1 1 1 VDD VCC 2 8 7 6 5 B0 B1 B2 B3

1 DS4

R4 10K

R3 10K

1 R2 10K

R36 10K 2 2

R37 10K

S1 4 position switch SWITCH (S1) IS OPTIONAL & DEFAULTED TO ALL OFF (OPEN)

C9 0.1uF

C4 0.1uF

C2 0.1uF

C10 0.1uF

C8 0.1uF

C12 0.1uF

C30 0.1uF

C3 0.1uF

C7 0.1uF

C11 0.1uF

ALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OF INTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THIS INFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TO BE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATED BY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESS CONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENT COVENANTS IT WILL NOT BE USED IN ANY MANNER DETRIMENTAL TO THE INTEREST OF IGT, AND MUST BE RETURNED ON DEMAND.

DRAWN

DATE

INTERNATIONAL GAME TECHNOLOGY

9295 PROTOTYPE DRIVE RENO, NV 89511

TITLE

SCHEMATIC PCB, 960 MULTI I/O

DWG. NO. REV LTR

DWG. SIZE

C

APPROVED

754 278 11

DATE

A

2 OF __ 2 SHT __

VSS

CHECKED

DATE

SCALE

T.D.WAXMAN

04MAY98

NONE

10

ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY)

AUGUST 24, 2001

Potrebbero piacerti anche

- Esquema Manager Net + Com BorneDocumento1 paginaEsquema Manager Net + Com BorneIrandy SousaNessuna valutazione finora

- Placa 1Documento1 paginaPlaca 1Juan Galarza100% (1)

- Aic 1084-33PMDocumento6 pagineAic 1084-33PMluismilenio3111Nessuna valutazione finora

- iPRO RC Operation and Maintenance Manual PDFDocumento146 pagineiPRO RC Operation and Maintenance Manual PDFJesus David GonzalezNessuna valutazione finora

- NES Famicom PinoutsDocumento1 paginaNES Famicom PinoutsgbyudbyNessuna valutazione finora

- Pinout of Most Common ConnectorsDocumento5 paginePinout of Most Common ConnectorsMatas SkirkevičiusNessuna valutazione finora

- lcd 主要参数速查表Documento30 paginelcd 主要参数速查表api-3821017100% (1)

- EchivalenteDocumento6 pagineEchivalenteteretaeNessuna valutazione finora

- KTL220S-Xx Service ManualDocumento37 pagineKTL220S-Xx Service ManualCamilo Ernesto Rodriguez RodriguezNessuna valutazione finora

- Aristocrat-Technical Bulletin SPC 2.5Documento2 pagineAristocrat-Technical Bulletin SPC 2.5johan cameloNessuna valutazione finora

- User Manual For DOWNGRADE PS4 Through The SYSGLITCH ProcedureDocumento6 pagineUser Manual For DOWNGRADE PS4 Through The SYSGLITCH ProcedureReceptores ServesNessuna valutazione finora

- Quick Tip: Serial Protocol Converter 2.5 (SPC2.5) Quick ReferenceDocumento2 pagineQuick Tip: Serial Protocol Converter 2.5 (SPC2.5) Quick ReferenceSergio Augusto Correa FierroNessuna valutazione finora

- MonitorsDocumento37 pagineMonitorsJorge Caceres100% (1)

- FL-03xx - User GuideDocumento82 pagineFL-03xx - User Guidezhekasxg100% (1)

- Spare Parts Catalog: 8 2007 Agi GMBH Wiener Strasse 158 A-2352 Gumpoldskirchen Austria Europe Tel.: +43-2252-606Documento34 pagineSpare Parts Catalog: 8 2007 Agi GMBH Wiener Strasse 158 A-2352 Gumpoldskirchen Austria Europe Tel.: +43-2252-606Mitica ScurtuNessuna valutazione finora

- Schematic Multi-Input Module WM8805Documento3 pagineSchematic Multi-Input Module WM8805aleksa64Nessuna valutazione finora

- Arduino SAS HostDocumento2 pagineArduino SAS HostOscar Javier Gomez0% (1)

- Dualshock 4: Digital CamouflageDocumento9 pagineDualshock 4: Digital Camouflagearfan lesmanaNessuna valutazione finora

- 555 Timer Principles - Revb3 PDFDocumento9 pagine555 Timer Principles - Revb3 PDFCA_KenNessuna valutazione finora

- LPC P2148 SchematicDocumento1 paginaLPC P2148 SchematicSagar Potdar100% (1)

- LPC1768 Board SchematicDocumento1 paginaLPC1768 Board Schematicshindo216100% (1)

- Coin Comparitor CompatibilityDocumento2 pagineCoin Comparitor CompatibilityWorldwide Gaming IncNessuna valutazione finora

- Spare Parts Catalog: Machine Type: Vip Iii 50 Gaming Platform: Various Game Software: VariousDocumento14 pagineSpare Parts Catalog: Machine Type: Vip Iii 50 Gaming Platform: Various Game Software: VariousMitica ScurtuNessuna valutazione finora

- Power Plant SchematicDocumento1 paginaPower Plant SchematicCippoNessuna valutazione finora

- The Helix XT Pushes The Boundaries of Technology, Offering A Seamless Portrait Gaming ExperienceDocumento2 pagineThe Helix XT Pushes The Boundaries of Technology, Offering A Seamless Portrait Gaming ExperienceenzolnNessuna valutazione finora

- Ds NV Quadro k1200 Feb15 NV Us HRDocumento1 paginaDs NV Quadro k1200 Feb15 NV Us HRJose PazNessuna valutazione finora

- 42HD (PPM42M6HSX) PDFDocumento6 pagine42HD (PPM42M6HSX) PDFMartín Sayago100% (1)

- Lenovo ThinkPad T460s BT460 NM-A421 Schematic DiagramDocumento99 pagineLenovo ThinkPad T460s BT460 NM-A421 Schematic DiagramАлександр ПетрыгаNessuna valutazione finora

- G5 Ministar Roulette Installation&Maintenance Manual v.1.2 PDFDocumento64 pagineG5 Ministar Roulette Installation&Maintenance Manual v.1.2 PDFSergey VissarionovNessuna valutazione finora

- CTK 4000Documento26 pagineCTK 4000JorgeBaquéNessuna valutazione finora

- Single Synchronous Buck Controller: RT8202/A/BDocumento18 pagineSingle Synchronous Buck Controller: RT8202/A/BMax ReparNessuna valutazione finora

- EC5462ADocumento11 pagineEC5462AstolllleNessuna valutazione finora

- Block Diagram: LGA 775-Pin SocketDocumento20 pagineBlock Diagram: LGA 775-Pin SocketRajesh DhanambalNessuna valutazione finora

- lcd1 PDFDocumento6 paginelcd1 PDFddvp_gunawardana100% (1)

- IGT Game King 044 Video CTRL Board Drawing Assy (757-044-10)Documento4 pagineIGT Game King 044 Video CTRL Board Drawing Assy (757-044-10)Turko Alejandro50% (2)

- Dell Inspiron n5110 m5110 Dq15 Wistron Queen 15 Intel Discrete Uma Sandy Bridge Rev A00 SCHDocumento108 pagineDell Inspiron n5110 m5110 Dq15 Wistron Queen 15 Intel Discrete Uma Sandy Bridge Rev A00 SCHMaula HassanNessuna valutazione finora

- Sony Vaio VPCEH2N1E MBX-247 Schematic Diagram Quanta HK1Documento39 pagineSony Vaio VPCEH2N1E MBX-247 Schematic Diagram Quanta HK1SRG InfoTechNessuna valutazione finora

- Unor3smbus 2.inoDocumento6 pagineUnor3smbus 2.inoM. Randy AswinNessuna valutazione finora

- ID03-001 (Rev05) Communication SpecDocumento36 pagineID03-001 (Rev05) Communication SpeckeskexNessuna valutazione finora

- MK8 SVMOD 0002 - PeripheralsDocumento48 pagineMK8 SVMOD 0002 - Peripheralswillian eduardo santiago cardenasNessuna valutazione finora

- Msi H81m-E33 MS-7817 Rev. 1.0Documento32 pagineMsi H81m-E33 MS-7817 Rev. 1.0GudangNessuna valutazione finora

- Mpu6 - Generic Horizon-manual-short-Form Issue 1.3 - No SafetyDocumento44 pagineMpu6 - Generic Horizon-manual-short-Form Issue 1.3 - No SafetyDean BurnsNessuna valutazione finora

- GM 338Documento56 pagineGM 338Muhammad Husein Dalimunthe0% (1)

- Williams 1995 Congo Parts ListDocumento74 pagineWilliams 1995 Congo Parts ListzokiNessuna valutazione finora

- Panasonic 2009 PDP TC-P54Z1 TC-P54V10 TC-P50V10 TC-P50G15 TC-P46G15 TC-P42G15 TC-P54G10 TC-P50G10 TC-P46G10 TC-P42G10 TC-P54S1 TC-P50S1 TC-P46S1 TC-P42S1 TCDocumento46 paginePanasonic 2009 PDP TC-P54Z1 TC-P54V10 TC-P50V10 TC-P50G15 TC-P46G15 TC-P42G15 TC-P54G10 TC-P50G10 TC-P46G10 TC-P42G10 TC-P54S1 TC-P50S1 TC-P46S1 TC-P42S1 TCedNessuna valutazione finora

- Mikromeia Board For PIC18FJDocumento2 pagineMikromeia Board For PIC18FJmorghabiNessuna valutazione finora

- Repair Manual For Universal Machine Power Supply (UMPS) (P/No 220010) Doc. No. 957-001 Revision A02Documento14 pagineRepair Manual For Universal Machine Power Supply (UMPS) (P/No 220010) Doc. No. 957-001 Revision A02German ParceroNessuna valutazione finora

- Ceronix Tech Training 050107Documento60 pagineCeronix Tech Training 050107Gloria Cecilia Bermudez ParraNessuna valutazione finora

- Toshiba Satellite L500D (Compal LA-4971P KSWAE Liverpool 10AR - 10ARG) PDFDocumento45 pagineToshiba Satellite L500D (Compal LA-4971P KSWAE Liverpool 10AR - 10ARG) PDFismaeltorresrojasNessuna valutazione finora

- Sanyo LCD 32XF7 Chasis UH6L Diagrama PDFDocumento2 pagineSanyo LCD 32XF7 Chasis UH6L Diagrama PDFLucía MitchellNessuna valutazione finora

- LB# 820-2849 Schematic Diagram PDFDocumento103 pagineLB# 820-2849 Schematic Diagram PDFHugo MansillaNessuna valutazione finora

- Soft Start SCHDocumento1 paginaSoft Start SCHTiwi Keromo100% (1)

- Information Provided byDocumento22 pagineInformation Provided byvico21hNessuna valutazione finora

- DOP7Documento2 pagineDOP7Nghia Do100% (1)

- Behringer Pmp6000 SCHDocumento15 pagineBehringer Pmp6000 SCHLuis PowerNessuna valutazione finora

- Nobreak Manger III - Onda SenoidalDocumento1 paginaNobreak Manger III - Onda SenoidalFenix Automação100% (1)

- Daewoo DVG 6000DDocumento12 pagineDaewoo DVG 6000DOssian Valera PinedaNessuna valutazione finora

- UltrasonicDocumento1 paginaUltrasonicNaman TamrakarNessuna valutazione finora

- W375 L3 V1.2 SchemDocumento3 pagineW375 L3 V1.2 SchemAdrian PeterNessuna valutazione finora

- ADV Main SchematicDocumento1 paginaADV Main Schematicgerardobrandao100% (1)

- MarketReview11 12 YuduDocumento92 pagineMarketReview11 12 Yuduvilla1960Nessuna valutazione finora

- User Manual Burning Bingo (ENG)Documento420 pagineUser Manual Burning Bingo (ENG)villa1960Nessuna valutazione finora

- Manual Software Basic Setup Atronic Cashline WBC Rev 2 0Documento46 pagineManual Software Basic Setup Atronic Cashline WBC Rev 2 0villa1960100% (1)

- SPC2 - Dual Port SetupDocumento2 pagineSPC2 - Dual Port Setupvilla1960Nessuna valutazione finora

- MK5PFC PCB MAIN 4362 Rev 7 Reference Designators C TopDocumento1 paginaMK5PFC PCB MAIN 4362 Rev 7 Reference Designators C Topvilla1960Nessuna valutazione finora

- 100 - HNGDocumento100 pagine100 - HNGvilla1960100% (1)

- OXYGEN™ Cabinet - Integration Guide For Player Tracking and Online Components 1.2Documento13 pagineOXYGEN™ Cabinet - Integration Guide For Player Tracking and Online Components 1.2villa1960Nessuna valutazione finora

- User Manual: Novo Touchbet™ Live-Roulette Version 4.6-25Documento270 pagineUser Manual: Novo Touchbet™ Live-Roulette Version 4.6-25villa1960100% (1)

- Manual FV623CF1Documento248 pagineManual FV623CF1edgarzg100% (3)

- Clear NovomaticDocumento1 paginaClear Novomaticvilla1960100% (4)

- Manual FV623CF1Documento248 pagineManual FV623CF1edgarzg100% (3)

- Manual Nv9Documento38 pagineManual Nv9villa1960Nessuna valutazione finora

- Assassins Creed Art BookDocumento75 pagineAssassins Creed Art BookGeorge GatsisNessuna valutazione finora

- Malnutrition Case StudyDocumento3 pagineMalnutrition Case Studyapi-622273373Nessuna valutazione finora

- Christine Remembered That Today Is The Birthday of Her BossDocumento1 paginaChristine Remembered That Today Is The Birthday of Her BossA.Nessuna valutazione finora

- ISA Guidelines PPF 1Documento19 pagineISA Guidelines PPF 1Vasu DevanNessuna valutazione finora

- 2009-04-CEN-TC121 N1574 Working Programme CEN TC 121Documento28 pagine2009-04-CEN-TC121 N1574 Working Programme CEN TC 121Manuel ValenteNessuna valutazione finora

- Pavlishchuck Addison - 2000 - Electrochemical PotentialsDocumento6 paginePavlishchuck Addison - 2000 - Electrochemical PotentialscomsianNessuna valutazione finora

- Bagi CHAPT 7 TUGAS INGGRIS W - YAHIEN PUTRIDocumento4 pagineBagi CHAPT 7 TUGAS INGGRIS W - YAHIEN PUTRIYahien PutriNessuna valutazione finora

- Marisa Wolf Final New ResumeDocumento2 pagineMarisa Wolf Final New Resumeapi-403499166Nessuna valutazione finora

- Homeopatia Vibracional RatesDocumento45 pagineHomeopatia Vibracional RatesAugusto Bd100% (4)

- SafetyStock OverviewDocumento3 pagineSafetyStock OverviewJosue FonsecaNessuna valutazione finora

- Structural Engineering Formulas Second EditionDocumento224 pagineStructural Engineering Formulas Second Editionahmed_60709595194% (33)

- Norman K. Denzin - The Cinematic Society - The Voyeur's Gaze (1995) PDFDocumento584 pagineNorman K. Denzin - The Cinematic Society - The Voyeur's Gaze (1995) PDFjuan guerra0% (1)

- Gita Ananda SDocumento10 pagineGita Ananda Srosaanggita76Nessuna valutazione finora

- CrumpleZonesSE (Edit)Documento12 pagineCrumpleZonesSE (Edit)Dah Unknown MarksmenNessuna valutazione finora

- The Senior High School in The Phillipines: The Way To The WorldDocumento5 pagineThe Senior High School in The Phillipines: The Way To The WorldRodel Ramos DaquioagNessuna valutazione finora

- High School Physics Rutherford Atom Lesson 27Documento4 pagineHigh School Physics Rutherford Atom Lesson 27John JohnsonNessuna valutazione finora

- HTML Editor 8Documento13 pagineHTML Editor 8Guru PrasadNessuna valutazione finora

- Language Loss in Waray: Ni Voltaire Q. UyzonDocumento23 pagineLanguage Loss in Waray: Ni Voltaire Q. UyzonMary Rose OmbrogNessuna valutazione finora

- Web Programming: GET / HTTP/1.1 ..Documento16 pagineWeb Programming: GET / HTTP/1.1 ..Alecu IlieNessuna valutazione finora

- Orange County Sheriff's Office SeaWorld Death Investigative ReportDocumento43 pagineOrange County Sheriff's Office SeaWorld Death Investigative ReportWESH2News100% (1)

- Valuing Construction Variation by Using PWA, FIDIC, ICWMF and CEDA Fluctuation Formula MechanismDocumento5 pagineValuing Construction Variation by Using PWA, FIDIC, ICWMF and CEDA Fluctuation Formula MechanismAzman YahayaNessuna valutazione finora

- Math Habits of MindDocumento12 pagineMath Habits of MindAzmi SallehNessuna valutazione finora

- Curriculum Vitae: Career ObjectiveDocumento3 pagineCurriculum Vitae: Career ObjectiveRākesh Rakhi100% (1)

- Design of A Low Cost Hydrostatic Bearing: Anthony Raymond WongDocumento77 pagineDesign of A Low Cost Hydrostatic Bearing: Anthony Raymond WongRogelio DiazNessuna valutazione finora

- Algorithm Design: Figure 1. Architecture Diagram For Greykite Library's Main Forecasting Algorithm, SilverkiteDocumento3 pagineAlgorithm Design: Figure 1. Architecture Diagram For Greykite Library's Main Forecasting Algorithm, Silverkitesiper34606Nessuna valutazione finora

- Periodicity Review SL KeyDocumento4 paginePeriodicity Review SL KeyYeyoung ParkNessuna valutazione finora

- Organic Food Business in India A Survey of CompaniDocumento19 pagineOrganic Food Business in India A Survey of CompaniShravan KemturNessuna valutazione finora

- Important Points in SurveyingDocumento4 pagineImportant Points in SurveyingAnand BossNessuna valutazione finora

- Earthing SystemsDocumento6 pagineEarthing SystemsRob PettitNessuna valutazione finora

- Understanding PumpDocumento113 pagineUnderstanding Pumpnyr1981_942955963100% (5)