Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

De0 Nano c4 Rev C (Release CD Rom)

Caricato da

Alexander LempelzivDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

De0 Nano c4 Rev C (Release CD Rom)

Caricato da

Alexander LempelzivCopyright:

Formati disponibili

5

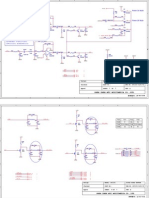

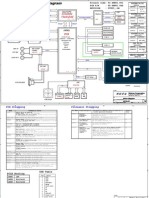

ALTERA Cyclone IV Development & Education Board (DE0-Nano)

D D

SCHEMATIC

01 TOP 02 EP4CE22 03 IN/OUT 04 MEMORY 05 POWER

C

CONTENT

Cover Page, Placement,TOP Cyclone IV EP4CE22 BANK1..BANK8 , POWER , CONFIG CLOCK, LED, BUTTON,SW, GPIOs, 2X13 HEADER, G-SENSOR, ADC SDRAM, EEPROM POWER 1.2V, 2.5V, 3.3V

PAGE

01 ~ 03 04 ~ 08 09 ~ 11 12 ~ 13 14

C

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number COVER PAGE Thursday, July 12, 2012 Sheet

1

Rev C 1 of 14

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number PLACEMENT Thursday, July 12, 2012 Sheet

1

Rev C 2 of 14

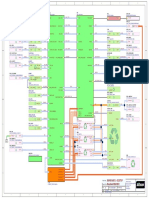

PAGE 4 - 8 DRAM_DQ[15..0] DRAM_ADDR[12..0] DRAM_DQM[1..0] DRAM_BA0 DRAM_BA1 DRAM_CAS_N DRAM_RAS_N DRAM_WE_N DRAM_CS_N DRAM_CKE DRAM_CLK CLOCK_50 KEY[1..0] I2C_SDAT I2C_SDAT SW[3..0] LED[7..0] 04 MEMORY I2C_SCLK I2C_SDAT G_SENSOR_CS_N G_SENSOR_INT ADC_SDAT ADC_CS_N ADC_SADDR ADC_SCLK DRAM_DQ[15..0] DRAM_ADDR[12..0] DRAM_DQM[1..0] DRAM_BA0 DRAM_BA1 DRAM_CAS_N DRAM_RAS_N DRAM_WE_N DRAM_CS_N DRAM_CKE DRAM_CLK CLOCK_50 KEY[1..0] SW[3..0] LED[7..0] I2C_SCLK I2C_SDAT G_SENSOR_CS_N G_SENSOR_INT ADC_SDAT ADC_CS_N ADC_SADDR ADC_SCLK 02 EP4CE22 TMS TCK TDI TDO NSTATUS CONF_DONE NCONFIG NCE JTAG_TMS JTAG_TCK JTAG_TDI JTAG_TDO NSTATUS CONF_DONE NCONFIG NCE I2C_SCLK I2C_SDAT G_SENSOR_CS_N G_SENSOR_INT GPIO_0_IN[1..0] GPIO_0[33..0] GPIO_1_IN[1..0] GPIO_1[33..0] GPIO_2_IN[2..0] GPIO_2[12..0] GPIO_0_IN[1..0] GPIO_0[33..0] GPIO_1_IN[1..0] GPIO_1[33..0] GPIO_2_IN[2..0] GPIO_2[12..0]

PAGE 9 - 11 GPIO_0_IN[1..0] GPIO_0[33..0] GPIO_1_IN[1..0] GPIO_1[33..0] GPIO_2_IN[2..0] GPIO_2[12..0] ADC_SDAT ADC_CS_N ADC_SADDR ADC_SCLK I2C_SCLK I2C_SDAT G_SENSOR_CS_N G_SENSOR_INT 03 IN/OUT PAGE 14 CLOCK_50 KEY[1..0] SW[3..0] LED[7..0] CLOCK_50 KEY[1..0] SW[3..0] LED[7..0]

PAGE 12 - 13 DRAM_ADDR[12..0] DRAM_DQM[1..0] DRAM_BA0 DRAM_BA1 DRAM_CAS_N DRAM_RAS_N DRAM_WE_N DRAM_CS_N DRAM_CKE DRAM_CLK I2C_SCLK DRAM_DQ[15..0]

DRAM_ADDR[12..0] DRAM_DQM[1..0] DRAM_BA0 DRAM_BA1 DRAM_CAS_N DRAM_RAS_N DRAM_WE_N DRAM_CS_N DRAM_CKE DRAM_CLK I2C_SCLK

DRAM_DQ[15..0]

ADC_SDAT ADC_CS_N ADC_SADDR ADC_SCLK

05 POWER

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number TOP Thursday, July 12, 2012 Sheet

1

Rev C 3 of 14

SW[3..0] DRAM_ADDR[12..0] DRAM_DQ[15..0] LED[7..0] KEY[1..0]

U1A LED6 DRAM_WE_N LED4 I2C_SCLK I2C_SDAT DRAM_DQ0 DRAM_DQ1 B1 C2 D1 F2 F1 G2 G1 DQS2L/CQ3L,CDPCLK0 DIFFIO_L3p DIFFIO_L4N DIFFIO_L5p DIFFIO_L5n DIFFIO_L6p/DQS0L/CQ1L,DPCLK0 DIFFIO_L6n IO1_0 IO/VREFB1N0 DRAM_DQ5 DRAM_DQ6 DRAM_DQ4 DRAM_DQ15 DRAM_RAS_N DRAM_CAS_N DRAM_ADDR10 DRAM_ADDR11 DRAM_ADDR0 DRAM_ADDR9 J2 J1 K2 K1 L2 L1 N2 N1 P2 P1

U1B DIFFIO_L7p/DQ1L IO2_0/DQS3L/CQ3L#,CDPCLK1 DIFFIO_L7n/DQ1L DIFFIO_L10p RUP1/DQ1L DIFFIO_L10n/DQ1L RDN1/DQ1L DIFFIO_L11p/DQS1L/CQ1L#,DPCLK1 DIFFIO_L11n/DQ1L IO/VREFB2N0 DIFFIO_L13p/DQ1L DIFFIO_13n/DQ1L DIFFIO_L15p/DQ1L DIFFIO_L15n/DM1L/BWS#1L CLK2/DIFFCLK_1p CLK3/DIFFCLK_1n R1 K5 L4 L3 DRAM_ADDR8 DRAM_DQ3 DRAM_ADDR12 LED7

C

G5 G_SENSOR_CS_N F3 LED5

M2 M1

G_SENSOR_INT SW0

BANK 1

CLK1/DIFFCLK_0n EP4CE22F17 E1 KEY1

BANK 2

EP4CE22F17

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number EP4CE22 BANK1 & BANK2 Thursday, July 12, 2012 Sheet

1

Rev C 4 of 14

SW[3..0] DRAM_ADDR[12..0]

D D

DRAM_DQ[15..0] GPIO_1[33..0] DRAM_DQM[1..0] GPIO_1_IN[1..0]

U1D U1C DRAM_DQ14 DRAM_DQ13 DRAM_DQ11 DRAM_DQ10 DRAM_ADDR1 DRAM_ADDR2 DRAM_BA0 DRAM_DQ12 DRAM_DQM1 DRAM_DQM0 DRAM_ADDR7 DRAM_DQ7 DRAM_ADDR5 DRAM_DQ2 DRAM_ADDR3 DRAM_ADDR6 DRAM_ADDR4 N3 P3 R3 T3 N5 N6 M7 R5 T5 R6 T6 R7 T7 L8 M8 N8 P8 DIFFIO_B1p IO3_0/DQS1B/CQ1B#,CDPCLK2 DIFFIO_B1n/DM3B/BWS#3B IO3_1/DQ3B DIFFIO_B2p/DQ3B IO3_2/DQ3B DIFFIO_B2n DIFFIO_B4p/DQ3B DIFFIO_B4n/DQ3B DIFFIO_B5p/DQS3B/CQ3B#,DPCLK2 DIFFIO_B6p/DQ3B IO/VREFB3N0 DIFFIO_B6n DIFFIO_B7p/DQ3B PLL1_CLKOUTp DIFFIO_B7n PLL1_CLKOUTn DIFFIO_B8p/DQ3B DIFFIO_B8n/DQS5B/CQ5B#,DPCLK3 DIFFIO_B9n/DQ3B DIFFIO_B10n/DM5B/BWS#5B CLK15/DIFFCLK_6p DIFFIO_B11p/DQ5B CLK14/DIFFCLK_6n DIFFIO_B12n/DQ5B T2 M6 L7 DRAM_DQ9 DRAM_BA1 DRAM_CKE GPIO_114 GPIO_111 GPIO_18 GPIO_19 GPIO_17 GPIO_16 GPIO_15 GPIO_14 GPIO_13 GPIO_12 GPIO_11 GPIO_112 N9 R10 T10 R11 T11 R12 T12 R13 T13 T14 T15 N12 DIFFIO_B14n/DQ5B IO4_0/DQS2B/CQ3B,DPCLK5 DIFFIO_B16p/DQ5B DIFFIO_B16n/DQS4B/CQ5B,DPCLK4 DIFFIO_B17p/DQ5B DIFFIO_B17n RUP2 DIFFIO_B18p/DQ5B RDN2 DIFFIO_B18n/DQ5B DIFFIO_B20p DIFFIO_B20n/DQ5B IO/VREFB4N0 DIFFIO_B23p/DQ5B DIFFIO_B23n/DQS0B/CQ1B,CDPCLK3 DIFFIO_B24p PLL4_CLKOUTp PLL4_CLKOUTn CLK13/DIFFCLK_7p CLK12/DIFFCLK_7n P9 GPIO_113

M10 N11 P11 P14 R14 R9 T9

GPIO_128 GPIO_115

C

P6 R4 T4

DRAM_CS_N DRAM_CLK DRAM_DQ8

GPIO_110 GPIO_125 GPIO_122 GPIO_1_IN1 GPIO_1_IN0

R8 T8

CLOCK_50 SW1

BANK 4

EP4CE22F17

BANK 3

EP4CE22F17

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number EP4CE22 BANK3 & BANK4 Thursday, July 12, 2012 Sheet

1

Rev C 5 of 14

KEY[1..0] GPIO_1[33..0] SW[3..0]

GPIO_2_IN[2..0] GPIO_2[12..0]

U1E GPIO_121 GPIO_118 GPIO_123 GPIO_124 GPIO_129 GPIO_116 GPIO_119 GPIO_117 GPIO_131 GPIO_130 KEY0 GPIO_133 GPIO_132 P16 R16 N16 N15 L13 L16 L15 K16 K15 J16 J15 J14 J13 DIFFIO_R15n/DQS3R/CQ3R#,CDPCLK4 DIFFIO_R15p/DQ1R DIFFIO_R13n/DQ1R DIFFIO_R13p/DQ1R DIFFIO_R12p/DQ1R DIFFIO_R11n/DQ1R DIFFIO_R11p RUP3/DM1R/BWS#1R DIFFIO_R10n/DQ1R RDN3/DQ1R DIFFIO_R10p/DQS1R/CQ1R#,DRCLK6 DIFFIO_R9n/DEV_OE DIFFIO_R9p/DEV_CLRn IO/VREFB5N0 DIFFIO_R8n/DQ1R DIFFIO_R7n/DQ1R CLK6/DIFFCLK_3p CLK7/DIFFCLK_3n GPIO_211 GPIO_212 GPIO_29 GPIO_28 GPIO_23 GPIO_24 N14 P15 L14 GPIO_127 GPIO_120 GPIO_126 G16 G15 F16 F15 C16 C15

U1F DIFFIO_R5n/INIT_DONE DIFFIO_R5p/CRC_ERROR DIFFIO_R4n/nCEO DIFFIO_R4p/CLKUSR DIFFIO_R1n/PADD20/DQS2R/CQ3R,CDPCLK5 DIFFIO_R1p IO6_0 IO6_1/DQS0R/CQ1R,DPCLK7 IO6_2 IO6_3/PADD23 IO/VREFB6N0 M15 M16 SW3 GPIO_2_IN2 EP4CE22F17

F13 B16 D16 D15 F14 E15 E16

GPIO_10 GPIO_21 GPIO_25 GPIO_26 GPIO_210 GPIO_2_IN0 GPIO_2_IN1

BANK 6

CLK4/DIFFCLK_2p CLK5/DIFFCLK_2n

BANK 5

EP4CE22F17

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number EP4CE22 BANK5 & BANK6 Thursday, July 12, 2012 Sheet

1

Rev C 6 of 14

LED[7..0] SW[3..0] GPIO_2[12..0] GPIO_0[33..0] GPIO_0_IN[1..0]

U1G GPIO_22 GPIO_27 GPIO_031 GPIO_032 LED1 LED2 GPIO_030 GPIO_033 LED3 GPIO_029 LED0 GPIO_022 ADC_CS_N ADC_SADDR GPIO_024 GPIO_025 GPIO_023 C14 D14 D11 D12 A13 B13 A12 B12 A11 B11 A15 F9 A10 B10 C9 D9 E9 DIFFIO_T24n RUP4 DIFFIO_T24p/DQ5T RDN4 DIFFIO_T23n DIFFIO_T23p/DQS0T/CQ1T,CDPCLK6 DIFFIO_T22n DIFFIO_T22p/DQ5T DIFFIO_T21n/DQ5T DIFFIO_T21p/DQ5T DIFFIO_T20n/DQ5T DIFFIO_T20p/PADD0/DQ5T IO/VREFB7N0 DIFFIO_T19n/PADD1 DIFFIO_T17p/PADD4/DQS2T/CQ3T,DPCLK8 DIFFIO_T16n/PADD5/DQ5T DIFFIO_T16p/PADD6/DQ5T PLL2_CLKOUTp DIFFIO_T15n/PADD7/DQ5T PLL2_CLKOUTn DIFFIO_T15p/PADD8/DM5T/BWS#5T DIFFIO_T13p/PADD12/DQS4T/CQ5T,DPCLK9 CLK9/DIFFCLK_5p CLK8/DIFFCLK_5n E11 E10 GPIO_026 GPIO_027 GPIO_016 GPIO_020 GPIO_021 GPIO_014 GPIO_012 GPIO_011 GPIO_010 GPIO_017 GPIO_08 GPIO_07 GPIO_013 GPIO_06 GPIO_05 GPIO_02 GPIO_03 C8 E8 F8 A7 B7 A6 B6 E6 A5 B5 D6 A4 B4 A2 A3

U1H DIFFIO_T11p/PADD17/DQS5T/CQ5T#,DPCLK10 DIFFIO_T10n/DATA2/DQ3T IO8_0/DQ3T DIFFIO_T10p/DATA3 IO8_1/DATA5/DQ3T DIFFIO_T9n/PADD18/DQ3T IO8_2 DIFFIO_T9p/DATA4/DQ3T IO8_3/DATA12 DIFFIO_T7n/DATA14/DQS3T/CQ3T#,DPCLK11 DIFFIO_T7p/DATA13/DQ3T DIFFIO_T6p/DATA6/DQ3T DIFFIO_T5n/DATA7/DQ3T IO/VREFB8N0 DIFFIO_T5p/DATA8/DQ3T DIFFIO_T4n/DATA9 DIFFIO_T3n/DATA10/DM3T/BWS#3T PLL3_CLKOUTp DIFFIO_T3p/DATA11 PLL3_CLKOUTn DIFFIO_T2n DIFFIO_T2p CLK11/DIFFCLK_4p CLK10/DIFFCLK_4n D8 E7 D5 B3 GPIO_019 GPIO_018 GPIO_09 GPIO_04

C

C6 D3 C3 B8 A8

GPIO_015 GPIO_00 GPIO_01 GPIO_0_IN1 GPIO_0_IN0

C11

GPIO_028

B14 A14

ADC_SCLK GPIO_20

BANK 8

B9 A9

SW2 ADC_SDAT EP4CE22F17

BANK 7

EP4CE22F17

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number EP4CE22 BANK7 & BANK8 Thursday, July 12, 2012 Sheet

1

Rev C 7 of 14

VCC1P2 VCC3P3 C1 100u K14 M14 E14 G14 A16 C10 C13 P10 P13 T16 K3 M3 E3 G3 U1I

D

VCC1P2

VCC1P2

VCC1P2

VCC1P2

VCC1P2

C2 2.2n

C3 2.2n

C4 4.7n

C5 4.7n

C6 10n

C7 10n

C8 0.47u

C9 0.47u

C10 0.1u

C11 0.1u

C12 0.1u

C13 0.1u

C14 0.1u

C15 0.1u

C16 0.1u

C17 0.1u

A1 C4 C7

P4 P7 T1

VCCIO1 VCCIO1

VCCIO2 VCCIO2

VCCIO3 VCCIO3 VCCIO3

VCCIO4 VCCIO4 VCCIO4

VCCIO5 VCCIO5

VCCIO6 VCCIO6

VCCIO7 VCCIO7 VCCIO7

VCCD_PLL N4 D13 D4 N13 F7 F11 G6 G7 G8 G9 G10 H6 H11 J6 K7 K11 L6 K9 K10 M9 M11 J12 L5 F12 F5 L12 VCCD_PLL1 VCCD_PLL2 VCCD_PLL3 VCCD_PLL4 VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCA1 VCCA2 VCCA3 VCCA4

VCCIO8 VCCIO8 VCCIO8

VCC3P3 GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GNDA1 GNDA2 GNDA3 GNDA4 E4 E13 G4 G13 K4 K13 M4 M13 N7 N10 P5 P12 R2 R15 E2 H16 H15 M5 E12 E5 M12

VCC3P3

VCC1P2

C18 100u

C19 0.1u

C20 0.1u

C21 0.1u

C22 0.1u

C23 0.1u

C24 0.1u

C25 0.1u

C26 0.1u

POWER & GND

VCCA

VCCD_PLL

C27 0.1u

C28 0.1u

C29 0.1u

C30 0.1u

C31 0.1u

C32 0.1u

C33 0.1u

C34 0.1u

VCCA

VCC2P5 GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND L1 EP4CE22F17

VCCA BEAD C35 10u

VCC1P2 L2

VCCD_PLL BEAD C36 10u VCC3P3 VCC3P3 U9 1 2 VCC 9 VCC 10 VCC GND EPCS64 R39 10K DNI Close to EPCS DATA DCLK nCS ASDI 8 16 7 15 R41 DCLK NCSO ASDO

B

H7 H8 H9 H10 J7 J8 J9 J10 F6 F10 J11 K8 K6 L9 L10 L11 K12 G11 B2 B15 C5 C12 D7 D10

24.9 DATA0

C89

B

VCCA

0.1u

VCCA U1J TCK R5 10K R6 10K TMS TDI R4 R7 1K DNI TBD DNI C37 TBD TCK TMS TDI TDO DCLK NSTATUS NCONFIG NCE TDO R11 DNI

A

R1 0 MSEL0 MSEL1 MSEL2 H13 H12 G12

R2 0 DNI

R3 0

H3 J5 H4 J4 H1 F4 H5 J3

TCK TMS TDI TDO DCLK nSTATUS nCONFIG nCE EP4CE22F17

CONFIGURATION

ASDO nCSO DATA0 CONF_DONE

AS Fast POR configuration at 3.0- or 2.5-V R8 C1 D2 H2 H14 ASDO NCSO DATA0 CONF_DONE 0 DNI R9 0 R10 0 DNI

1K

VCCA

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number EP4CE22 POWER and CONFIGURATION Thursday, July 12, 2012 Sheet

1

Rev C 8 of 14

LED[7..0]

LED0

D

LEDG

D

LED0 LED1 LED2 LED3

RN1 1 2 3 4

120 8 7 6 5

LED1 LED2 LED3

LEDG VCC3P3 LEDG LEDG C38 1 0.1u 2 Y1 EN GND 50MHZ VCC OUT 4 3 CLOCK_50

LED4 LED4 LED5 LED6 LED7 RN2 1 2 3 4 120 8 7 6 5 LED5 LED6 LED7

C

LEDG LEDG LEDG

VCC3P3 LEDG 8 7 6 5 SW[3..0] RN3 10K VCC2P5 SW1

ON

R12 100K KEY0 4 1 3 VCC2P5 2 C39 1n 2K 14 1 3 5 9 11 13 U2 VCC 1A 2A 3A 4A 5A 6A ETP 1Y 2Y 3Y 4Y 5Y 6Y GND 15 2 4 6 8 10 12 7 TACK_SW_RA R13

VCC2P5 C41 0.1u

1 2 3 4

8 7 6 5

1 2 3 4

SW0 SW1 SW2 SW3

SW-DIP8

KEY0 KEY1

B

KEY[1..0]

VCC2P5

SN74AUC17 R14 100K KEY1 4 1 3 2 C40 1n 2K R15

TACK_SW_RA

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number CLOCK & LED & BUTTON & SWITCH Thursday, July 12, 2012 Sheet

1

Rev C 9 of 14

GPIO_0[33..0] GPIO_0_IN[1..0]

GPIO_1[33..0] GPIO_1_IN[1..0]

GPIO - 0 JP1 GPIO_0_IN0 GPIO_0_IN1 GPIO_02 GPIO_04 GPIO_06 VCC_SYS GPIO_08 GPIO_010 GPIO_012 GPIO_014 GPIO_016 GPIO_018 GPIO_020 GPIO_022 GPIO_024 GPIO_026 GPIO_028 GPIO_030 GPIO_032 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 GPIO_00 GPIO_01 GPIO_03 GPIO_05 GPIO_07 GPIO_09 GPIO_011 GPIO_013 GPIO_015 GPIO_017 GPIO_019 GPIO_021 GPIO_023 GPIO_025 GPIO_027 GPIO_029 GPIO_031 GPIO_033 VCC_SYS GPIO_1_IN0 GPIO_1_IN1 GPIO_12 GPIO_14 GPIO_16 GPIO_18 GPIO_110 GPIO_112 GPIO_114 GPIO_116 GPIO_118 GPIO_120 GPIO_122 GPIO_124 GPIO_126 GPIO_128 GPIO_130 GPIO_132 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39

GPIO - 1 JP2 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 GPIO_10 GPIO_11 GPIO_13 GPIO_15 GPIO_17 GPIO_19 GPIO_111 GPIO_113 GPIO_115 GPIO_117 GPIO_119 GPIO_121 GPIO_123 GPIO_125 GPIO_127 GPIO_129 GPIO_131 GPIO_133

VCC3P3

VCC3P3

GPIO_2[12..0] GPIO_2_IN[2..0] Analog_In[7..0] GPIO - 2 JP3 VCC3P3 GPIO_2_IN1 GPIO_20 GPIO_22 GPIO_24 GPIO_26 GPIO_28 GPIO_210 GPIO_212 Analog_In6 Analog_In3 Analog_In4 Analog_In1 1 3 5 7 9 11 13 15 17 19 21 23 25 1 3 5 7 9 11 13 15 17 19 21 23 25 2 4 6 8 10 12 14 16 18 20 22 24 26 2 4 6 8 10 12 14 16 18 20 22 24 26 GPIO_2_IN0 GPIO_2_IN2 GPIO_21 GPIO_23 GPIO_25 GPIO_27 GPIO_29 GPIO_211 Analog_In5 Analog_In7 Analog_In2 Analog_In0

2X13 HEADER

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number GPIOs & 2X13 Header Thursday, July 12, 2012 Sheet

1

Rev C 10 of 14

VCC3P3_VA R16 Analog_In[7..0] C42 1u C43 0.1u 49.9

VCC3P3

C44 1u

C45 0.1u

VCC3P3

Digital Accelerometer

Analog_In0 R17 22 C46 1n U3 1 2 3 4 5 6 7 VDD GND RESERVED GND GND VS CS_n SCL_SCLK SDA_SDI_SDIO SDO_ALT_ADDRESS RESERVED_1 NC INT2 INT1 ADXL345 G_SENSOR_INT C50 1n AGND 14 13 12 11 10 9 8 I2C_SCLK I2C_SDAT R19 R62 DNI 0 R21 DNI 2.2K AGND Analog_In2 R22 22 ADC_IN2 1n ADC_IN0 VCC3P3 AGND 10K Analog_In1 R20 22 C48 ADC_IN1

AGND

AGND VCC3P3_VA VCC3P3

VCC_VS

13 VD

R18 DNI

C

U4 1 14 15 16 ADC_CS_N ADC_SADDR ADC_SDAT ADC_SCLK

C47 G_SENSOR_CS_N C49

1u

0.1u

VCC_VS

ADC_IN0 ADC_IN1 ADC_IN2 ADC_IN3 ADC_IN4 ADC_IN5 ADC_IN6 ADC_IN7

4 5 6 7 8 9 10 11

VA

2.2K

IN0 IN1 IN2 IN3 IN4 IN5 IN6 IN7 AGND

CS_n DIN DOUT SCLK

DGND 12 L4 ADC128S022CIMTX BEAD AGND

VCC3P3

VCC_VS VCC_VS

Analog_In3

R24

22 C51

ADC_IN3 AGND 1n

L3

BEAD

C52 4.7u

C53 0.1u Analog_In4 R25 22 C54 1n AGND Analog_In5 R26 22 C55 1n AGND Analog_In6 R27 22 C56 1n AGND Analog_In7 R28 22 C57 1n Title AGND Size B Date:

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

AGND ADC_IN4

B

ADC_IN5

ADC_IN6

ADC_IN7

A

DE0-Nano Board

Document Number G-Sensor & ADC Thursday, July 12, 2012 Sheet

1

Rev C 11 of 14

DRAM_DQ[15..0]

D

DRAM_ADDR[12..0] DRAM_DQM[1..0] 1 14 27 U5

VCC3P3

D

VDD VDD VDD

DRAM_ADDR0 DRAM_ADDR1 DRAM_ADDR2 DRAM_ADDR3 DRAM_ADDR4 DRAM_ADDR5 DRAM_ADDR6 DRAM_ADDR7 DRAM_ADDR8 DRAM_ADDR9 DRAM_ADDR10 DRAM_ADDR11 DRAM_ADDR12 DRAM_CLK DRAM_CKE DRAM_DQM0 DRAM_DQM1 DRAM_WE_N DRAM_CAS_N DRAM_RAS_N DRAM_CS_N DRAM_BA0 DRAM_BA1

23 24 25 26 29 30 31 32 33 34 22 35 36 38 37 15 39 16 17 18 19 20 21

VDDQ VDDQ VDDQ VDDQ

3 9 43 49

A0 D0 A1 D1 A2 D2 A3 D3 A4 D4 A5 D5 A6 D6 A7 D7 A8 D8 A9 D9 A10 D10 A11 SDRAM 16Mx16 D11 A12 D12 CLK D13 CKE D14 LDQM D15 UDQM nWE nCAS nRAS nCS BA0 BA1 VSS VSS VSS

2 4 5 7 8 10 11 13 42 44 45 47 48 50 51 53

DRAM_DQ0 DRAM_DQ1 DRAM_DQ2 DRAM_DQ3 DRAM_DQ4 DRAM_DQ5 DRAM_DQ6 DRAM_DQ7 DRAM_DQ8 DRAM_DQ9 DRAM_DQ10 DRAM_DQ11 DRAM_DQ12 DRAM_DQ13 DRAM_DQ14 DRAM_DQ15

6 12 46 52

28 41 54

VSSQ VSSQ VSSQ VSSQ

VCC3P3

C58 0.1u

C59 0.1u

C60 0.1u

C61 0.1u

C62 0.1u

C63 0.1u

C64 0.1u

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size A Date:

5 4 3

Document Number SDRAM Thursday, July 12, 2012

2

Rev C Sheet 12

1

of

14

VCC3P3 VCC3P3

R29 0 DNI

C

R30 0 DNI

R31 0 DNI 1 2 3 4

VCC3P3 U6 A0 A1 A2 VSS 9 VCC WP SCL SDA 8 7 6 5

R32 2K

R33 2K I2C_SCLK I2C_SDAT

VCC3P3 C65 0.1u

C

R34 1K

R35 1K

24LC02B R36 1K I2C ADDRESS W/R = 0xA0/0xA1

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size A Date:

5 4 3

Document Number EEPROM Thursday, July 12, 2012

2

Rev C Sheet 13

1

of

14

5V Power from USB Port

VCC5_USB D5 PMEG2010AEB

VCC_SYS R60 J1 1 2 SIP2 DNI C66 10u 0 2 3 4

REG1 IN IN IN GND DAP OUT OUT OUT ADJ 7 6 5 C67 8 R37 5.36K 10u

VCC3P3

3.3V/1.5A

C68 0.1u VCC3P3 R38 1.2K

D

D6 PMEG2010AEB JP4 1 2 Power - HDR D8 D7 PMEG2010AEB

1 9

LP38500SD-ADJ

R40 120

Input Power Range: 3.6 ~ 5.7 V

PMEG2010AEB

VCC_SYS Range: 3.3 ~ 5.5 V

D2

POWER

VCC3P3 1 2 3 4 1X4 HEADER R46 J6 C69 DNI 1 2 3 4 1X4 HEADER VCC1P2 VCC3P3 0.47u R47 10K 4 VEN GND 0 6 VIN VOUT NC1 NC2 PAD 1 2 5 C70 0.47u C71 0.1u VCC2P5 VCC_SYS DNI R45 0 REG2

LEDB

J5

DNI

2.5V/150mA

LP5900SD-2.5

VCC3P3 MH1 MH2 MH3 MH4 C73 10u FID1 FID2 FID3 FID4 FID5 FID6 FID7 FID8 R61 J2 1 SIP2 DNI 2 0 2 3 4

REG3 IN IN IN GND DAP OUT OUT OUT ADJ 7 6 5 C72 8 R48 4.99K 10u

VCC1P2

1.2V/1.5A

C74 0.1u

1 9

LP38500SD-ADJ

R49 4.99K

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size B Date:

5 4 3 2

Document Number 1.2V & 2.5V & 3.3V Thursday, July 12, 2012 Sheet

1

Rev C 14 of 14

Potrebbero piacerti anche

- Engineering Service Revenues World Summary: Market Values & Financials by CountryDa EverandEngineering Service Revenues World Summary: Market Values & Financials by CountryNessuna valutazione finora

- M57TE V1.4: Rev. Date Description RemarkDocumento9 pagineM57TE V1.4: Rev. Date Description RemarkjmkcbeNessuna valutazione finora

- Shuttle B10ie01 - 71rb10ie0-9ha0 - T8a0 - Rev ADocumento23 pagineShuttle B10ie01 - 71rb10ie0-9ha0 - T8a0 - Rev AJoão Luis N. Do AmaralNessuna valutazione finora

- CCTV Surveillance: Video Practices and TechnologyDa EverandCCTV Surveillance: Video Practices and TechnologyValutazione: 4 su 5 stelle4/5 (1)

- BRD2201A A02 SchematicDocumento10 pagineBRD2201A A02 Schematickunalkundanam1046Nessuna valutazione finora

- Practical Embedded Controllers: Design and Troubleshooting with the Motorola 68HC11Da EverandPractical Embedded Controllers: Design and Troubleshooting with the Motorola 68HC11Nessuna valutazione finora

- Clevo W243HUQ W244HUQ 6-7P-W24H5-002 WWW - MYCOMP.SUDocumento42 pagineClevo W243HUQ W244HUQ 6-7P-W24H5-002 WWW - MYCOMP.SURafaNotes SmartsNessuna valutazione finora

- Samsung Sch-A410 Service ManualDocumento30 pagineSamsung Sch-A410 Service Manualsaboor ashraf100% (1)

- MTK 6218 SchematicsDocumento5 pagineMTK 6218 SchematicssajjadfattahNessuna valutazione finora

- DE0 ReleaseDocumento19 pagineDE0 Releasedoniz30Nessuna valutazione finora

- Beginning Arduino Nano 33 IoT: Step-By-Step Internet of Things ProjectsDa EverandBeginning Arduino Nano 33 IoT: Step-By-Step Internet of Things ProjectsNessuna valutazione finora

- P+5V P+5V: Power On MuteDocumento8 pagineP+5V P+5V: Power On MuteuyrikNessuna valutazione finora

- Radio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142Da EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142Nessuna valutazione finora

- Ts 4900 Schematic PDFDocumento7 pagineTs 4900 Schematic PDFPrashanth KumarNessuna valutazione finora

- A14IEXX Positivo UniqueDocumento26 pagineA14IEXX Positivo UniqueJhonatan KalitaNessuna valutazione finora

- Acer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHDocumento67 pagineAcer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHWilgen GarciaNessuna valutazione finora

- Cy2 Fpga Starter Board SchematicDocumento21 pagineCy2 Fpga Starter Board SchematicFerry HidayatNessuna valutazione finora

- Arduino Yun SchematicDocumento7 pagineArduino Yun SchematicgetmicrosNessuna valutazione finora

- TM 7043Documento13 pagineTM 7043Radek KurekNessuna valutazione finora

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsDa EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsValutazione: 1 su 5 stelle1/5 (1)

- At3u Si 0502aDocumento37 pagineAt3u Si 0502aAshok JangraNessuna valutazione finora

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationDa EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNessuna valutazione finora

- Hawkboard Schematics v1Documento11 pagineHawkboard Schematics v1Sam KhawseNessuna valutazione finora

- Beginning STM32: Developing with FreeRTOS, libopencm3 and GCCDa EverandBeginning STM32: Developing with FreeRTOS, libopencm3 and GCCNessuna valutazione finora

- Samsung GT-C3322 Metro Duos SchematicsDocumento3 pagineSamsung GT-C3322 Metro Duos SchematicsTerry MetamorfosaNessuna valutazione finora

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosDa EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosValutazione: 5 su 5 stelle5/5 (1)

- Scheme-Hp Pavilion Dv5 - Intel Qt6Documento44 pagineScheme-Hp Pavilion Dv5 - Intel Qt6sergeybezrNessuna valutazione finora

- Marine Machinery, Equipment & Supplies Wholesale Revenues World Summary: Market Values & Financials by CountryDa EverandMarine Machinery, Equipment & Supplies Wholesale Revenues World Summary: Market Values & Financials by CountryNessuna valutazione finora

- Ak1 MB 1213aDocumento30 pagineAk1 MB 1213aAshok JangraNessuna valutazione finora

- PIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsDa EverandPIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsValutazione: 5 su 5 stelle5/5 (1)

- Samsung GT-E3210 08 Level 3 Repair - Block-, PCB Diagrams, Flow Chart of TroubleshootingDocumento38 pagineSamsung GT-E3210 08 Level 3 Repair - Block-, PCB Diagrams, Flow Chart of TroubleshootingAmat Sofiyan100% (1)

- Acer Aspire-5510 Schematic DiagramDocumento40 pagineAcer Aspire-5510 Schematic DiagramAbubakar SidikNessuna valutazione finora

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCDa EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNessuna valutazione finora

- MCD Demo2 Manual enDocumento33 pagineMCD Demo2 Manual enmario_villarreal_110% (1)

- Pickit 2 Clone SMDDocumento6 paginePickit 2 Clone SMDJoc AntNessuna valutazione finora

- The New 3D Layout for Oil & Gas Offshore Projects: How to ensure successDa EverandThe New 3D Layout for Oil & Gas Offshore Projects: How to ensure successValutazione: 4.5 su 5 stelle4.5/5 (3)

- Smoothieboard 5driver SchematicDocumento4 pagineSmoothieboard 5driver SchematicdududadamikeNessuna valutazione finora

- Fluidic Components and Equipment 1968–9: Pergamon Electronics Data SeriesDa EverandFluidic Components and Equipment 1968–9: Pergamon Electronics Data SeriesNessuna valutazione finora

- Albion: Index - Alb522MbDocumento18 pagineAlbion: Index - Alb522MbShauna MooreNessuna valutazione finora

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemDa EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNessuna valutazione finora

- Tomtom One XL SchematicDocumento11 pagineTomtom One XL Schematicsuysuy00100% (1)

- LG r510 - Quanta Ql8 Tw8 - Rev 3asecDocumento41 pagineLG r510 - Quanta Ql8 Tw8 - Rev 3asecGerson SoaresNessuna valutazione finora

- DCT700 ph0Documento14 pagineDCT700 ph0waltech2005100% (1)

- HP Compaq Presario Cq61 Quanta Op6 Op7 Tango Ballet Rev A SCHDocumento37 pagineHP Compaq Presario Cq61 Quanta Op6 Op7 Tango Ballet Rev A SCHHugo G.Nessuna valutazione finora

- Un32c5000 - 40C5000 - 46C5000 MainDocumento16 pagineUn32c5000 - 40C5000 - 46C5000 Mainmj15015Nessuna valutazione finora

- Acer I5 47501306462469980Documento67 pagineAcer I5 47501306462469980fdsaq12Nessuna valutazione finora

- So Do Nb2dsk01Documento72 pagineSo Do Nb2dsk01maithuong85Nessuna valutazione finora

- Intel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197AklftDocumento50 pagineIntel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197Aklftdrop9721Nessuna valutazione finora

- Ts 7500 SchematicDocumento4 pagineTs 7500 Schematicimransiddiquiatvxt100% (1)

- 5000 RM-362/RM-363 Service Manual Level 1&2Documento0 pagine5000 RM-362/RM-363 Service Manual Level 1&2Alexander LempelzivNessuna valutazione finora

- Stratocaster Service ManualDocumento4 pagineStratocaster Service ManualAlexander LempelzivNessuna valutazione finora

- Flash ProgrammingDocumento5 pagineFlash ProgrammingAlexander LempelzivNessuna valutazione finora

- Altera De0-NanoDocumento153 pagineAltera De0-NanoAlexander LempelzivNessuna valutazione finora

- Life Evolution Universe Lecture Notes - AUCDocumento45 pagineLife Evolution Universe Lecture Notes - AUCAlejandro VerdeNessuna valutazione finora

- TRG TRC001 en PsychrometryDocumento89 pagineTRG TRC001 en PsychrometryhonismeNessuna valutazione finora

- Cloud Computing 101 TutorialDocumento203 pagineCloud Computing 101 TutorialYunis Iklil100% (1)

- Methley Railway Station: A Proposal To The Department For Transport.Documento38 pagineMethley Railway Station: A Proposal To The Department For Transport.Rt Hon. Alec Shelbrooke, M.P.0% (1)

- Overcoming Obstacles To Ethical BehaviourDocumento4 pagineOvercoming Obstacles To Ethical BehaviourSimran SinghNessuna valutazione finora

- Energy Epp1924 WildlifeAndAssetProtection EnglishDocumento56 pagineEnergy Epp1924 WildlifeAndAssetProtection EnglishFalquian De EleniumNessuna valutazione finora

- Saudi Arabia Companies Contact DetailsDocumento64 pagineSaudi Arabia Companies Contact DetailsYAGHMOURE ABDALRAHMAN86% (69)

- Vr31a OmDocumento5 pagineVr31a OmrudydanielleNessuna valutazione finora

- Checklist For Rebar and Concrete WorkDocumento4 pagineChecklist For Rebar and Concrete WorkDwinto RachmadNessuna valutazione finora

- Nature'S Numbers: - BasicbooksDocumento39 pagineNature'S Numbers: - Basicbooksyeol pacisNessuna valutazione finora

- 1663-43691010-Me-Dwg-7380-00-Cu-Cl2-Bdu-Fru-Assy-1 (R1)Documento1 pagina1663-43691010-Me-Dwg-7380-00-Cu-Cl2-Bdu-Fru-Assy-1 (R1)raacontreras21Nessuna valutazione finora

- Star WarsDocumento28 pagineStar Warsalex1971Nessuna valutazione finora

- Shallow FoundationsDocumento44 pagineShallow FoundationsAjay SinghNessuna valutazione finora

- EE 720 - HW Set 3 - 1Documento2 pagineEE 720 - HW Set 3 - 1Abdullah AL-RazemNessuna valutazione finora

- The Child's Learning of English Morphology: WORDDocumento29 pagineThe Child's Learning of English Morphology: WORDCatnis TomNessuna valutazione finora

- PlumbingDocumento1 paginaPlumbingminesdomieNessuna valutazione finora

- KrautKramer DM4E DM4DL - ManualDocumento38 pagineKrautKramer DM4E DM4DL - ManualfdsgfdgNessuna valutazione finora

- BITS Pilani: Scale Up and Post Approval ChangesDocumento56 pagineBITS Pilani: Scale Up and Post Approval ChangesshrikantmsdNessuna valutazione finora

- Audio Level Meter - ProjectDocumento4 pagineAudio Level Meter - ProjectMircea PanzariuNessuna valutazione finora

- CSE 473 Pattern Recognition: Instructor: Dr. Md. Monirul IslamDocumento57 pagineCSE 473 Pattern Recognition: Instructor: Dr. Md. Monirul IslamNadia Anjum100% (1)

- Internship Report PDFDocumento11 pagineInternship Report PDFASWIN KUMARNessuna valutazione finora

- Usama Lab 6Documento8 pagineUsama Lab 6M mubeen riazNessuna valutazione finora

- P16mba7 1Documento4 pagineP16mba7 1Vishalatchi MNessuna valutazione finora

- ISMR B-School BrochureDocumento28 pagineISMR B-School Brochurerahul kantNessuna valutazione finora

- Lecture Note On Photovoltaic CellDocumento1 paginaLecture Note On Photovoltaic CellHaseeb NawazNessuna valutazione finora

- Avanti II 04-05Documento137 pagineAvanti II 04-05Donald SimsNessuna valutazione finora

- Eng Essay For PresentationDocumento8 pagineEng Essay For Presentationctn batrisyiaNessuna valutazione finora

- SOM-based Generating of Association RulesDocumento5 pagineSOM-based Generating of Association RulesKishor PeddiNessuna valutazione finora

- SVC200Documento5 pagineSVC200fransiskus_ricky3329Nessuna valutazione finora