Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

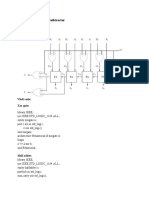

VHDL Code For Carry Save Adder

Caricato da

Anishkumar AyyaswamyDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

VHDL Code For Carry Save Adder

Caricato da

Anishkumar AyyaswamyCopyright:

Formati disponibili

VHDL Code For Carry Save Adder

Done By

Atchyuth Sonti

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL;

entity main is port( a:in std_logic_vector(3 downto 0); b:in std_logic_vector(3 downto 0); carry:in std_logic; outsum:out std_logic_vector(3 downto 0); outcarry:out std_logic); end main;

architecture Behavioral of main is signal c0,c1,sum0,sum1:std_logic_vector(3 downto 0); signal carry0,carry1:std_logic; component fulladder is port(a,b,cin :in std_logic; sum,cout: out std_logic); end component; begin carry0<=carry; carry1<=not carry; fa01:fulladder port map(a(0),b(0),carry0,sum0(0),c0(0));

fa02:fulladder port map(a(1),b(1),c0(0),sum0(1),c0(1)); fa03:fulladder port map(a(2),b(2),c0(1),sum0(2),c0(2)); fa04:fulladder port map(a(3),b(3),c0(2),sum0(3),c0(3)); fa11:fulladder port map(a(0),b(0),carry1,sum1(0),c1(0)); fa12:fulladder port map(a(1),b(1),c1(0),sum1(1),c1(1)); fa13:fulladder port map(a(2),b(2),c1(1),sum1(2),c1(2)); fa14:fulladder port map(a(3),b(3),c1(2),sum1(3),c1(3)); process(carry) begin if(carry='0') then outcarry<=c0(3); outsum<=sum0; else outcarry<=c1(3); outsum<=sum1; end if; end process; end Behavioral;

Sub Program For Full Adder

library IEEE; use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all;

entity fulladder is Port ( a : in STD_LOGIC; b : in STD_LOGIC; cin : in STD_LOGIC; sum : out STD_LOGIC; cout : out STD_LOGIC); end fulladder;

architecture Behavioral of fulladder is

begin sum<= a xor b xor cin; cout<=(a and b)or(b and cin)or(cin and a); end Behavioral;

Potrebbero piacerti anche

- Sol Ex010 11-Sã©rie2Documento6 pagineSol Ex010 11-Sã©rie2cncr87kffkNessuna valutazione finora

- ContohVHDL PartI II TugasDocumento55 pagineContohVHDL PartI II TugasLuthfiyah13Nessuna valutazione finora

- Library IEEE Use IEEE - STD - LOGIC - 1164.ALLDocumento4 pagineLibrary IEEE Use IEEE - STD - LOGIC - 1164.ALLJaspreet KaurNessuna valutazione finora

- VHDL Lab FileDocumento48 pagineVHDL Lab FileAnkit Gupta100% (1)

- Coding:: VHDL Code For BufferDocumento27 pagineCoding:: VHDL Code For BufferAar Kay GautamNessuna valutazione finora

- Exp No: 01 Verification of Logic Gates AimDocumento54 pagineExp No: 01 Verification of Logic Gates AimDivya ChanduriNessuna valutazione finora

- Library IEEEDocumento4 pagineLibrary IEEEAdeel HanifNessuna valutazione finora

- Comparateur 1bit StructurelleDocumento5 pagineComparateur 1bit StructurelleMohamed ChamessNessuna valutazione finora

- VhdlfileDocumento7 pagineVhdlfileNaveen NegiNessuna valutazione finora

- Fa Structure ModellingDocumento3 pagineFa Structure ModellingdineshvhavalNessuna valutazione finora

- VHDL ReportDocumento29 pagineVHDL ReportSalman AliNessuna valutazione finora

- Digital Lab Cs 6211 VHDL ProgramsDocumento13 pagineDigital Lab Cs 6211 VHDL ProgramsMurugan GNessuna valutazione finora

- Project 1 Carry Look Ahead AdderDocumento8 pagineProject 1 Carry Look Ahead AdderMansi JaisinghNessuna valutazione finora

- DISEÑODocumento1 paginaDISEÑOJose Montiel PulidoNessuna valutazione finora

- VHDL Code For Full AdderDocumento5 pagineVHDL Code For Full AdderVinod Kumarrockz100% (1)

- VHDL Code For Halfadder: - Logic - XorDocumento30 pagineVHDL Code For Halfadder: - Logic - XorAnushNessuna valutazione finora

- Ee529 Lab Asg4Documento10 pagineEe529 Lab Asg4dd23015Nessuna valutazione finora

- UNIT-3: Design Combinational CKT Using Architecture ModelDocumento36 pagineUNIT-3: Design Combinational CKT Using Architecture Modelankit_4382Nessuna valutazione finora

- Experiment 6: Adder/subtractor Block Diagram:: VHDL Code: Xor GateDocumento7 pagineExperiment 6: Adder/subtractor Block Diagram:: VHDL Code: Xor Gatepadmavasavi1973Nessuna valutazione finora

- Ejemplo Con Procedure: Archivo de TestbenchDocumento2 pagineEjemplo Con Procedure: Archivo de TestbenchrolandoNessuna valutazione finora

- Ejemplo Procedure PDFDocumento2 pagineEjemplo Procedure PDFrolandoNessuna valutazione finora

- INFORME PRACTICA No 2Documento30 pagineINFORME PRACTICA No 2MAURICIO REYES ROSERONessuna valutazione finora

- VHDL CompleteDocumento21 pagineVHDL CompleteMridanku Shekhar PramanickNessuna valutazione finora

- VHDL Code For Half Adder by Data Flow ModellingDocumento14 pagineVHDL Code For Half Adder by Data Flow ModellingPrateekKumar96% (24)

- The VHDL Hardware Description Language: CSEE W4840Documento31 pagineThe VHDL Hardware Description Language: CSEE W4840ankit bansalNessuna valutazione finora

- BCD Sumador de 1 Dígito: Library Use All Use All Entity Is Port in Downto in Out Downto Out End Architecture of IsDocumento3 pagineBCD Sumador de 1 Dígito: Library Use All Use All Entity Is Port in Downto in Out Downto Out End Architecture of IsCristian Fabian Romero RojasNessuna valutazione finora

- VHDL BasicsDocumento21 pagineVHDL BasicsPriya PriyaNessuna valutazione finora

- VHDL ProgramDocumento5 pagineVHDL ProgramJaswanth TejaNessuna valutazione finora

- VHDL Code For 4-Bit RcaDocumento2 pagineVHDL Code For 4-Bit Rcaajuklm88Nessuna valutazione finora

- Register-Transfer Level Design Register-Transfer Level (RTL) Is A Design Abstraction Which Models A Synchronous DigitalDocumento11 pagineRegister-Transfer Level Design Register-Transfer Level (RTL) Is A Design Abstraction Which Models A Synchronous Digitalmuru54321Nessuna valutazione finora

- Engr2015 Lab2Documento13 pagineEngr2015 Lab2SUPER AMAZINGNessuna valutazione finora

- Ieee Ieee STD - Logic - 1164 STD - Logic - Vector STD - Logic STD - LogicDocumento1 paginaIeee Ieee STD - Logic - 1164 STD - Logic - Vector STD - Logic STD - Logicnarayananmeera07Nessuna valutazione finora

- Labsheet 1: 1) Write VHDL Program To Model BASIC DIGITAL GATES and Simulate The Following Using MODELSIM CodeDocumento24 pagineLabsheet 1: 1) Write VHDL Program To Model BASIC DIGITAL GATES and Simulate The Following Using MODELSIM CodesachinpnNessuna valutazione finora

- VHDL Sample PtogramsDocumento40 pagineVHDL Sample PtogramsShanmuga PriyaNessuna valutazione finora

- LabDocumento4 pagineLabSouvik PalNessuna valutazione finora

- 4 Bit Ripple Carry Adder VHDL CodeDocumento5 pagine4 Bit Ripple Carry Adder VHDL CodeSwifty SpotNessuna valutazione finora

- EXOR Gate Using Concurrent Statements: RTL ViewDocumento59 pagineEXOR Gate Using Concurrent Statements: RTL ViewSurbhit SinhaNessuna valutazione finora

- Adder CompoDocumento4 pagineAdder Compobhslegion1498Nessuna valutazione finora

- Modeling Scheme.: Objective 1: VHDL Code For 2 Input XOR Gate Using BehavioralDocumento24 pagineModeling Scheme.: Objective 1: VHDL Code For 2 Input XOR Gate Using BehavioralAmrinder SinghNessuna valutazione finora

- Date: 28 September, 2015: VHDL Assighment 2Documento15 pagineDate: 28 September, 2015: VHDL Assighment 2Ishan DarwhekarNessuna valutazione finora

- VHDL Unit - 1Documento10 pagineVHDL Unit - 1hemanthperreddy123Nessuna valutazione finora

- HDL Lab ManualDocumento29 pagineHDL Lab ManualRaveen GulipuraNessuna valutazione finora

- Design A Half Adder Using Dataflow Architecture in VHDL Code (Autorecovered)Documento14 pagineDesign A Half Adder Using Dataflow Architecture in VHDL Code (Autorecovered)Amit SahaNessuna valutazione finora

- VHDL Mansi (1) MDocumento28 pagineVHDL Mansi (1) MMansi Jaisingh100% (1)

- Half Adder-1 PDFDocumento5 pagineHalf Adder-1 PDFر' حيلNessuna valutazione finora

- Digital Signals and DesignDocumento27 pagineDigital Signals and DesignkannNessuna valutazione finora

- Deber Digitales Nombre: Jossuet Farfan A. Codigo VHDLDocumento7 pagineDeber Digitales Nombre: Jossuet Farfan A. Codigo VHDLJossuet GallagherNessuna valutazione finora

- VHDL ManualDocumento19 pagineVHDL ManualDr.B.Krishna KumarNessuna valutazione finora

- VHDLDocumento17 pagineVHDLanilkumawat04Nessuna valutazione finora

- L7 Slides 2Documento40 pagineL7 Slides 2Amit SahaNessuna valutazione finora

- Sumador Completo Bloque VHDLDocumento4 pagineSumador Completo Bloque VHDLranduNessuna valutazione finora

- Code Converters and Comparator: Exp No: 05Documento12 pagineCode Converters and Comparator: Exp No: 05hahemeb608Nessuna valutazione finora

- MohamedSamir AssignmentDocumento45 pagineMohamedSamir Assignmentmohamed samierNessuna valutazione finora

- Computer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringDocumento71 pagineComputer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringSankhadeep ChakrabartiNessuna valutazione finora

- 8bit MiniproDocumento7 pagine8bit MiniprodemononesNessuna valutazione finora

- Correction VHDL ExercicesDocumento10 pagineCorrection VHDL ExercicesHazem HaNessuna valutazione finora

- Projects With Microcontrollers And PICCDa EverandProjects With Microcontrollers And PICCValutazione: 5 su 5 stelle5/5 (1)